## <u>Electronics – 2019 June</u>

| 1. |     | /42/M/J/19/No.8 A conducting sphere is mounted on an insulating stand. Explain how you would use positively charged rod of insulating material to charge the sphere by induction. | e a |

|----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|    |     |                                                                                                                                                                                   |     |

|    |     |                                                                                                                                                                                   |     |

|    |     |                                                                                                                                                                                   |     |

|    |     |                                                                                                                                                                                   |     |

|    |     |                                                                                                                                                                                   | [3] |

|    | (b) | Fig. 8.1 shows an electronic component.                                                                                                                                           |     |

|    |     | Fig. 8.1                                                                                                                                                                          |     |

|    |     | Otata the many of the common out above in Fig. 9.4                                                                                                                                | [4] |

|    |     | State the name of the component shown in Fig. 8.1                                                                                                                                 | [1] |

|    | (c) | In the space below, write down the truth table for a NAND gate.                                                                                                                   |     |

|    |     | Palo                                                                                                                                                                              |     |

|    |     |                                                                                                                                                                                   | [2] |

|    |     |                                                                                                                                                                                   |     |

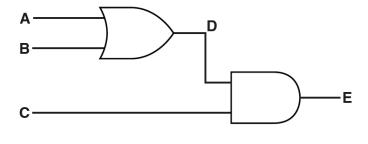

(d) Fig. 8.2 shows the connections to two logic gates.

Fig. 8.2

Table 8.1 shows part of the truth table for the arrangement of logic gates in Fig. 8.2.

Complete Table 8.1 for the input values shown.

Table 8.1

|   | inputs |    | intermediate<br>point | output |

|---|--------|----|-----------------------|--------|

| Α | В      | С  | D                     | E      |

| 0 | 0      | 1  |                       |        |

| 0 | 1      | 10 |                       |        |

| 1 | 1      | 0  |                       |        |

| 1 | 1      | 1  |                       |        |

[3]

[Total: 9]

| 2. | 0625/43/M/J/19/No.9    |  |

|----|------------------------|--|

|    | 0020/40/141/3/17/140.7 |  |

(a) Fig. 9.1 shows an electrical component.

Fig. 9.1

State the name of the component shown in Fig. 9.1. ......[1]

(b) In the space below, write down the truth table for a NOR gate.

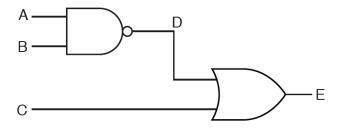

(c) Fig. 9.2 shows the connections between two logic gates.

Fig. 9.2

Complete the truth table shown in Table 9.1 for this combination of logic gates.

Table 9.1

|   | inputs |   | intermediate<br>point | output |

|---|--------|---|-----------------------|--------|

| Α | В      | С | D 🔩                   | O E    |

| 0 | 1      | 1 |                       |        |

| 1 | 0      | 1 | 2                     |        |

| 1 | 1      | 0 |                       |        |

| 1 | 1      | 1 | 0.                    |        |

[3]

| d) | Referring to a simple electron model, state what distinguishes electrical conductors from electrical insulators. |

|----|------------------------------------------------------------------------------------------------------------------|

|    |                                                                                                                  |

|    |                                                                                                                  |

|    |                                                                                                                  |

|    | [1]                                                                                                              |

|    | [1]                                                                                                              |

[Total: 7]