## <u>Electronics – 2021 IGCSE 0625</u>

## **1.** June/2021/Paper\_21/No.33

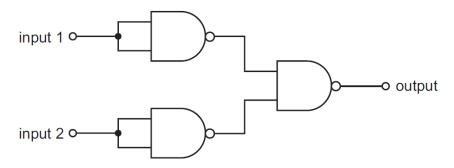

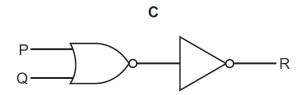

Three NAND gates are connected in a single chip as shown.

The whole chip behaves as a single logic gate.

Which type of logic gate does the chip act as?

- **A** AND gate

- В NAND gate

- С NOR gate

- D OR gate

## **2.** June/2021/Paper\_22/No.34

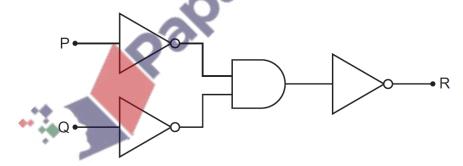

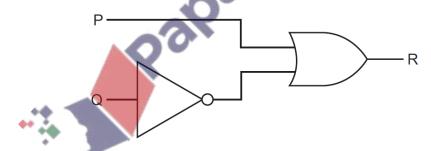

amoridoe The diagram shows a combination of four logic gates that produce an output signal at R that depends on the states of the inputs P and Q.

Which single logic gate produces the same effect as the combination?

- **A** AND

- В NAND

- C NOR

- D OR

# **3.** June/2021/Paper\_23/No.33

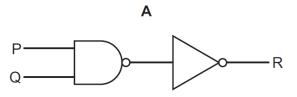

Which combination of two gates will result in the truth table shown?

| Р | Q | R |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

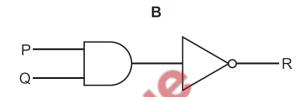

**4.** March/2021/Paper\_22/No.35

The circuit shown contains two gates.

Which truth table describes the operation of the circuit?

|   | Α |   |

|---|---|---|

| Р | Q | R |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

|   | В |   |

|---|---|---|

| Р | Q | R |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

|   | C |   |

|---|---|---|

| Р | Q | R |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

|   | D |   |

|---|---|---|

| Р | Q | R |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

# **5.** June/2021/Paper\_43/No.8

(a) State the difference between an analogue signal and a digital signal. You may draw a diagram to help explain your answer.

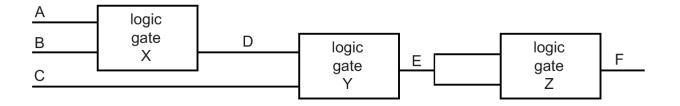

(c) Fig. 8.1 shows a combination of logic gates X, Y and Z. The gates are not represented by the standard symbols.

Fig. 8.1

Table 8.1 shows a partly completed truth table for this combination of logic gates.

Table 8.1

| inputs |   | intermediate points |   | output |   |

|--------|---|---------------------|---|--------|---|

| Α      | В | С                   | D | Е      | F |

| 0      | 0 | 0                   | 0 | 0 🦠    | 0 |

| 0      | 1 | 0                   | 0 | 0      |   |

| 1      | 0 | 1                   | 0 | 1      |   |

| 1      | 1 | 1                   | 1 | 1      |   |

| 0      | 0 | 0                   | 0 | 0      |   |

| 0      | 1 | 0                   | 0 | 0      |   |

| 1      | 0 | <b>O</b> 1          | 0 | 1      |   |

| 1      | 1 | 1                   | 1 | 1      |   |

- (i) From Table 8.1, deduce:

- 1. the name of logic gate X

.....[1]

2. the name of logic gate Y.

.....[1]

(ii) Logic gate Z is a NAND gate.

Complete column F of Table 8.1. [2]

[Total: 7]

| 6. March/2 | 2021/Paper | 42/No.9 |

|------------|------------|---------|

|------------|------------|---------|

(a) Write down the truth table for an OR gate.

[2]

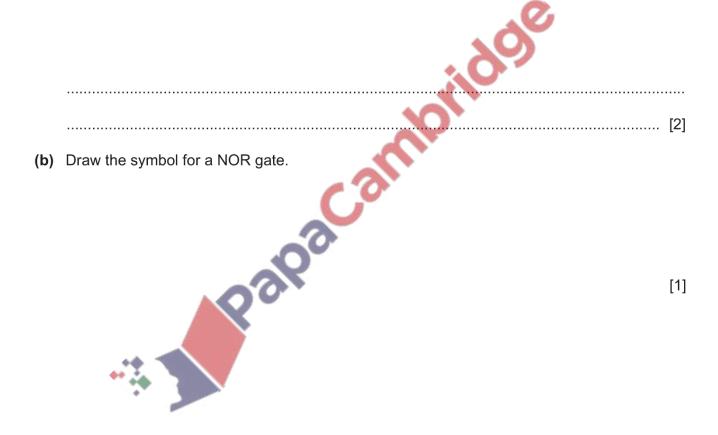

(b) Draw the symbol for a NOR gate.

[1]

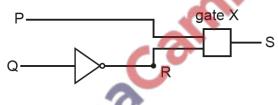

(c) Fig. 9.1 shows a digital circuit designed to produce the values shown in Table 9.1 for the output S from the two inputs P and Q.

Fig. 9.1

(i) Table 9.1 is the truth table for the circuit shown in Fig. 9.1.

Table 9.1

|     | -dd |

|-----|-----|

| . 7 |     |

| **  |     |

|     |     |

| P | Q | R | S |

|---|---|---|---|

| 0 | 0 |   | 0 |

| 0 | 1 |   | 0 |

| 1 | 0 |   | 1 |

| 1 | 1 |   | 0 |

Complete the column for point R in Table 9.1.

[1]

| i) | State which type of gate is used for gate X. Explain your answer. |

|----|-------------------------------------------------------------------|

|    | statement                                                         |

|    | explanation                                                       |

|    |                                                                   |

|    |                                                                   |

|    | اری                                                               |

|    | [Total: 7]                                                        |