# 1.3.2 Computer Architecture For IGCSE

# Chapter 4

# 1.3.2 Computer Architecture

Describe the stages of the fetch-execute cycle

| 10  |

|-----|

|     |

|     |

| 001 |

|     |

|     |

| *** |

| *** |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

| 10  |

|-----|

|     |

|     |

| 001 |

|     |

|     |

| *** |

| *** |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

|     |

| 201 |

|-----|

|     |

| CO. |

| 20  |

| 100 |

|     |

| *** |

|     |

|     |

|     |

|     |

|     |

|     |

| . 01 |

|------|

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

| **   |

| ***  |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

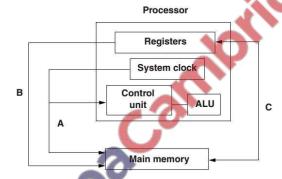

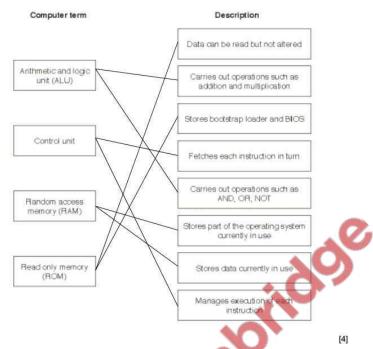

# **Von Neumann Architecture**

The idea about how computers should be built was proposed by John von Neumann in 1945.

Von Neumann gave an idea how to build computer. This idea is also called the von Neumann

# Architecture or Model.

A computer should have input/output devices, Arithmetic Logic Unit (ALU), Control Unit (CU) and computer memory (storage device).

Firstly programs should be stored in computer's memory (storage devices). From storage devices programs should be loaded into CPU (ALU & CU) for execution.

This is still the basis for computers today.

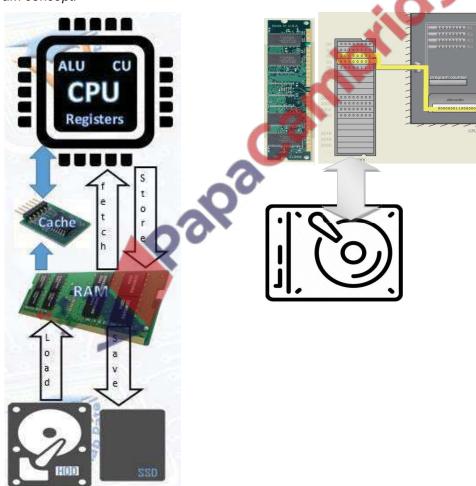

# **Stored Program Concept:**

The idea given by von Neumann, according to this concept computer should have storage device to store data and instruction to be processed. Data and instructions are first stored in secondary storage (HDD or SSD). Then they are loaded in main memory (RAM. Form main memory data and instructions are fetched in registers inside CPU. Decoder of CU decodes the instruction and ALU executes the instructions and results are stored firstly in main memory and then in secondary storage.

# Examiner Comments on Question to explain Stored Program Concept

This question appeared to be very challenging for candidates. Many candidates described the fetch execute cycle. It would be helpful if candidates understood that the stored program concept is a specific infrastructure for the central processing unit and not the fetch execute cycle. It would be encouraging to see candidates demonstrate a more confident level of knowledge of the stored program concept.

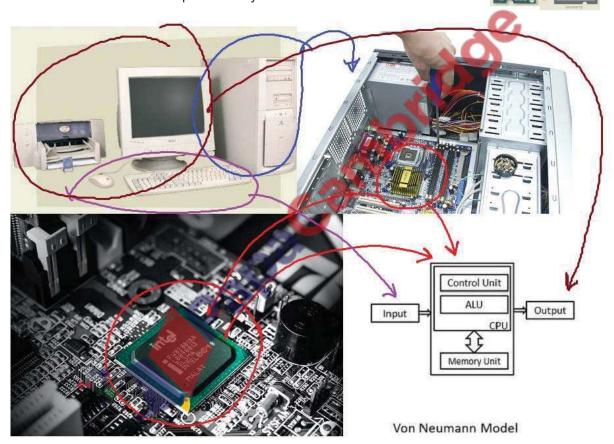

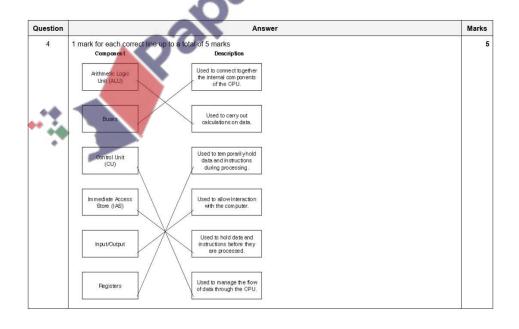

# Components of von Neumann Model

Von Neumann Model has following four components:

- 1. Input/Output Devices

- 2. Memory Unit

- 3. Control Unit

- 4. Arithmetic Logic Unit

# Input/output (I/O) Devices

The Input/output (I/O) components of a computer are hardware devices that are responsible for getting data from the computer to the user or from the user to the computer.

Data going from the user to the computer is called "input." The two main input devices are the mouse and the keyboard.

Output devices are used to transmit data from the computer's memory to the user. The two output devices almost every computer system has are the monitor and the printer.

# **Memory Unit**

Computer has several types of memory. Memory unit in the Von Neumann model is the main memory, also called RAM or Random Access Memory. It also refers as Immediate Access Store (IAS).

Immediate Access Store (i.e. main memory) holds data and instructions when they are waiting to be processed.

What distinguishes a computer from a calculator is the ability to run a stored program; main memory allows the computer to do that.

RAM can be thought of as a sequence of boxes, called cells, each of which can hold a certain amount of data. The remaining three components of the von Neumann model of a computer are found inside the Processor.

### **Control Unit**

The control unit controls the sequencing and timing of all operations. It contains a "clock," that is actually a quartz crystal that vibrates million times per second. The clock emits an electronic signal for each vibration. Each separate operation is synchronized to the clock signal. For example 1<sup>st</sup> pc operates at 4.7 MHz means 4.7 million instructions per second.

The functions of CU are given below:

- Interprets and carries out instruction of program.

- Selects program statements from memory.

- Moves these instructions to instruction registers

- Carries out instructions

- Directs flow of data between components of CPU and to and from other devices.

# Arithmetic & Logic Unit (ALU)

Arithmetic unit perform arithmetical operations like +, -, \*, and / while logical unit are to compare two quantities. Logical operations are important in computer programming.

ALU can be thought of as being similar to a calculator, except that, in addition to normal math, it can also do logical (true/false) operations.

The functions of ALU are given below:

- The arithmetic unit carries out arithmetic like addition, division.

- The logic unit enables the processor to make comparison like =, <, > and logical decisions like

AND, OR, NOT.

- The arithmetic logic unit carries out communication with peripheral devices.

- It also carries out bit shifting operation.

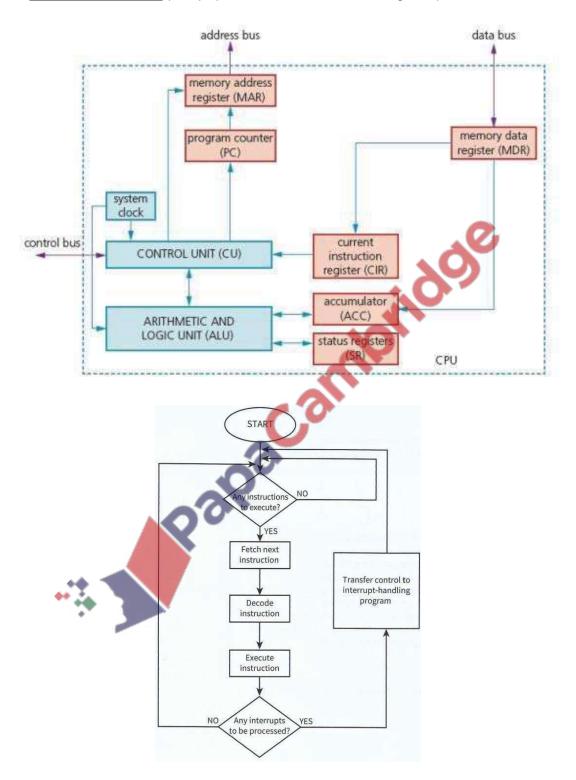

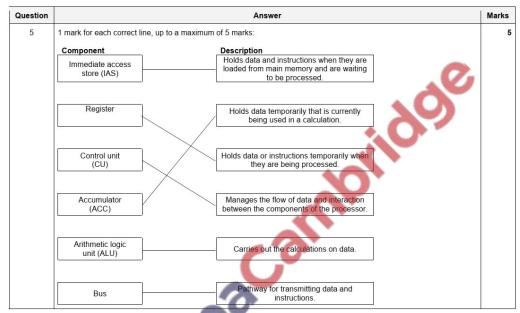

### Register:

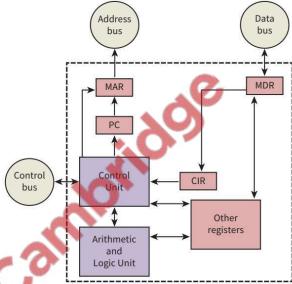

Registers are located on the CPU, and used temporarily for storing data. Because the registers are close to the ALU, they are made out of fast memory, efficiently speeding up calculations.

Registers store data fetched from Immediate Access Store i.e. main memory.

Immediate Access Store (i.e. main memory) holds data and instructions when they are waiting to be processed.

Register Holds data or instructions temporarily when they are being processed.

There are 16 registers. Some examples are

- a) <u>Program Counter</u> (PC) an incrementing counter that keeps track of the <u>next memory</u> address of the instruction that is to be executed once the execution of the current instruction is completed.

- b) <u>Memory Address Register</u> (MAR) the address in main memory that is currently being read or written

- c) <u>Memory Buffer/Data Register</u> (MBR/MBR) a two-way register that holds data fetched from memory (and ready for the CPU to process) or data waiting to be stored in memory

- d) <u>Current Instruction register</u> (CIR) a temporary holding ground for the instruction that has just been fetched from memory

- e) <u>Accumulator Register (ACC)</u> is used for storing data for ALU to process and the results those are produced by the ALU.

Buses: "The set of wires used to travel signals to and from CPU and different components of

computer is called Bus."

Bus is a group of parallel wires that is used as a communication path. As a wire transmits a single bit so 8-bits bus can transfer 8 bits (1 byte) at a time and 16-bits bus can transfer 16 bits (2 bytes) and so on. There are three types of buses according to three types of signals, these are:

- a) <u>Data Bus:</u> "The buses which are used to transmit data between CPU, memory and peripherals are called Data Bus."

- b) Address Bus: "The buses which are connecting the CPU with main memory and used to identify particular locations (address) in main memory where data is stored are called Address Buses."

- c) <u>Control Bus:</u> The wires which are used to transmit the control signals (instructions) generated by Control Unit to the relevant component of the computer.

# **Example Question**

**Q 4.1** (a) One of the key features of von Neumann computer architecture is the use of buses. Three buses and three descriptions are shown below. Draw a line to connect each bus to its correct description.

Address bus

Control bus

Data bus

This bus carries signals used to coordinate the computer's activities

This bi-directional bus is used to exchange data between processor, memory and input/ output devices

This uni-directional bus carries signals relating to memory addresses between processor and memory

# Q 4.2)

The diagram above shows a simplified form of processor architecture.

Name the three buses labelled A, B and C.

| В | A |     |

|---|---|-----|

|   | D |     |

|   | 0 | [0] |

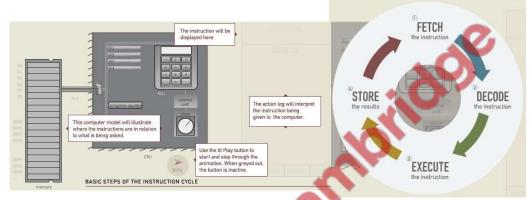

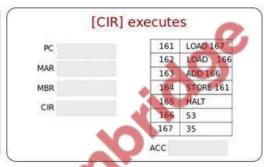

# **Fetch-Execute Cycle:**

At its core, all the computer ever does is, execute one instruction in memory after another, over and over. Although there are many different possible (assembly language) instructions that the computer can execute, the basic steps involved in executing an instruction are always the same, and they are called the instruction cycle.

- 1. **Fetch** the instruction (transfer the instruction from main memory to the decoder)

- 2. **Decode** the instruction (from machine language)

- 3. **Execute** the instruction (e.g., add, divide, load, store...)

- 4. **Store** the result (for instructions like ADD, place the 'answer' in the specified register.)

The control unit guides the computer's components through this cycle to execute one instruction. When that instruction is done, the cycle starts all over again with the next instruction.

# Registers/circuits involved

The circuits used in the CPU during the cycle are:

- <u>Program Counter</u> (PC) an incrementing counter that keeps track of the next memory address of the instruction that is to be executed once the execution of the current instruction is completed.

- Memory Address Register (MAR) the address in main memory that is currently being read or written

- Memory Buffer Register (MBR) a two-way register that holds data fetched from memory (and ready for the CPU to process) or data waiting to be stored in memory

- <u>Current Instruction register</u> (CIR) a temporary holding ground for the instruction that has just been fetched from memory

- <u>Accumulator Register (ACC)</u> is used for storing data for ALU to process and the results those are produced by the ALU.

- <u>Control Unit</u> (CU) decodes the program instruction in the CIR, selecting machine resources such as a data source register and a particular arithmetic operation, and coordinates activation of those resources

• Arithmetic logic unit (ALU) - performs mathematical and logical operations

# Fill in the following table

| Description               | PC | MAR | MDR | CIR | Decoder | ACC | ALU |

|---------------------------|----|-----|-----|-----|---------|-----|-----|

|                           |    |     |     |     |         |     |     |

|                           |    |     |     |     |         |     |     |

|                           |    |     |     |     |         |     |     |

|                           |    |     |     |     |         |     |     |

|                           |    |     |     |     |         |     |     |

|                           |    |     |     |     |         |     |     |

|                           |    |     |     |     |         |     |     |

|                           |    |     |     |     |         |     |     |

|                           |    |     |     |     |         |     |     |

|                           |    |     |     |     |         |     |     |

|                           |    |     |     |     | 0       |     |     |

|                           |    |     |     | *   |         |     |     |

|                           |    |     |     | 4   |         |     |     |

|                           |    |     | V   |     |         |     |     |

|                           |    |     |     |     |         |     |     |

|                           |    |     | 0.  |     |         |     |     |

|                           |    | 49  |     |     |         |     |     |

|                           |    |     |     |     |         |     |     |

|                           |    |     |     |     |         |     |     |

| est Yourself The table sh |    |     |     |     |         |     |     |

Put the stages into the correct sequence by writing the numbers 1 to 6 in the right hand column.[6]

| Description of stage                                                          | Sequence No |

|-------------------------------------------------------------------------------|-------------|

| the instruction is copied from the Memory Data Register (MDR) and placed      |             |

| in the Current Instruction Register (CIR)                                     |             |

| the instruction is executed                                                   |             |

| the instruction is decoded                                                    |             |

| the address contained in the Program Counter (PC) is copied to the Memory     |             |

| Address Register (MAR)                                                        |             |

| the value in the Program Counter (PC) is incremented so that it points to the |             |

| next instruction to be fetched                                                |             |

| the instruction is copied from the memory location contained in the Memory    |             |

| Address Register (MAR) and is placed in the Memory Data Register (MDR)        |             |

|                                                                               |             |

Register Transfer Notation

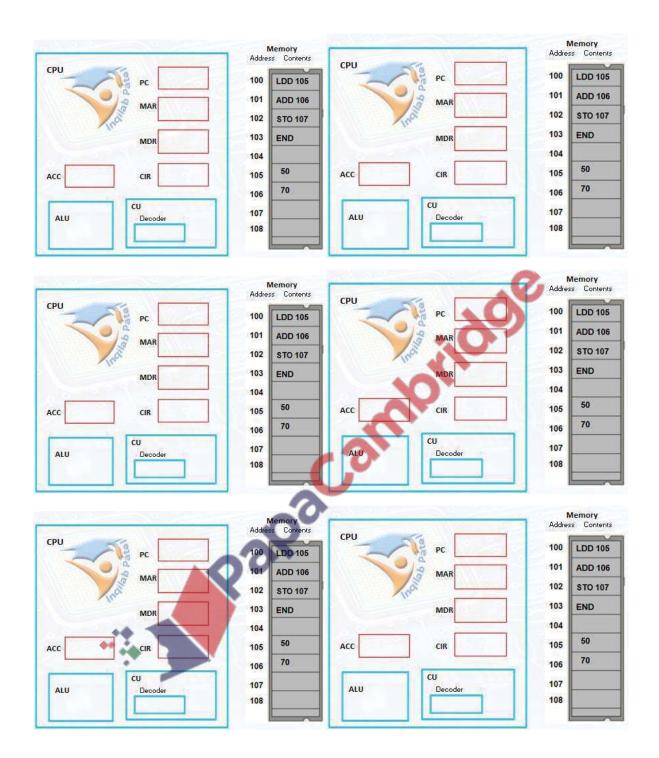

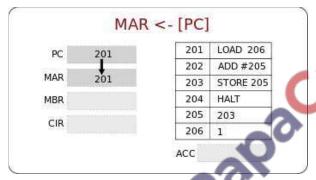

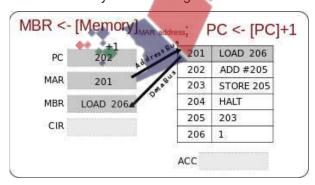

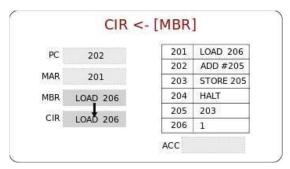

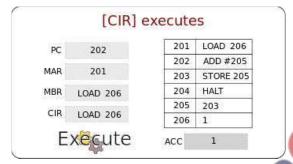

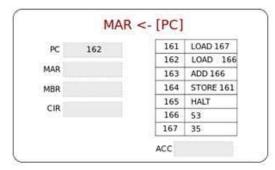

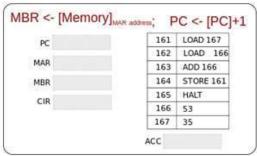

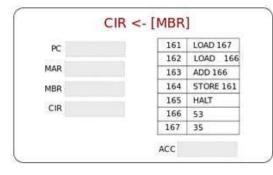

To describe the cycle we can use register notation. This is a very simple way of noting all the steps involved. In all cases brackets e.g. [PC], means that the contents of the thing inside the brackets are loaded. In the case of the first line, the contents of the program counter are loaded into the Memory Address Register.

MAR ← [PC]

MBR ← [Memory]; PC← [PC] +1 (Increment the PC for next cycle at the same time)

CIR ← [MBR]

CIR sends instruction to Decoder of control unit

Decoder decodes

Or ACC← [MBR]

ACC sends data to ALU

**ALU** executes

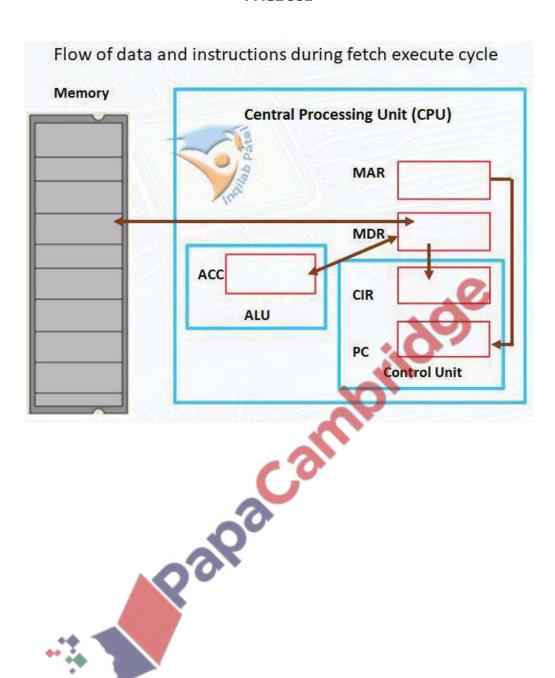

# **Detailed description of Fetch-Decode-Execute Cycle**

To better understand what is going on at each stage we'll now look at a detailed description:

The contents of the Program Counter, the address of the next instruction to be executed, is placed into the Memory Address Register

The address is sent from the MAR along the address bus to the Main Memory. The instruction at that address is found and returned along the data bus to the Memory Buffer Register. At the same time the contents of the Program Counter is increased by 1, to reference the next instruction to be executed.

The MBR loads the Current Instruction Register with the instruction to be decoded by decoder of control unit or the MBR loads Accumulator with the data to be executed.

The instruction is decoded and executed using the ALU if necessary.

The Cycle starts again!

Q 4.4a) Complete the following diagrams showing each step of the fetch decode execute cycle:

- b) The fetch-execute cycle is shown in register transfer notation.

- 01 MAR ←[PC]

- 02 PC ←[PC] 1

- 03 MDR ←[MAR]

- 04 CIR ←[MAR]

- (a) There are three errors in the fetch-execute cycle shown.

Identify the line number of each error and give the correction.

| Line number |      |      |         |

|-------------|------|------|---------|

| Correction  |      | <br> | <br>    |

| Line number | <br> | <br> | <br>    |

| Correction  |      | <br> | <br>    |

| Line number | <br> | <br> | <br>    |

| Correction  | <br> | <br> | <br>[3] |

# c) Solve the program shown below:

| Address | Contents |      |  |  |  |

|---------|----------|------|--|--|--|

| 1       | 1010 LDA | 1111 |  |  |  |

| 10      | 1111 ADD | 1110 |  |  |  |

| 11      | 0000 SUB | 1101 |  |  |  |

| 100     | 1111 ADD | 1100 |  |  |  |

| 101     | 1111 ADD | 1011 |  |  |  |

| 110     | 0000 SUB | #5   |  |  |  |

| 111     | 1111 ADD | #90  |  |  |  |

| 1000    | 0111 STO | 1010 |  |  |  |

| 1001    | 1100 S   | TP   |  |  |  |

| 1010    |          |      |  |  |  |

| 1011    | 55       |      |  |  |  |

| 1100    | 10       |      |  |  |  |

| 1101    | 5        |      |  |  |  |

| 1110    | 50       |      |  |  |  |

| 1111    | 150      |      |  |  |  |

| Keys: |     |

|-------|-----|

| 1010  | LDA |

| 1111  | ADD |

| 0     | SUB |

| 111   | STO |

| 1100  | STP |

| 000  | 0111 STO    | 101 | 0   |     |          |          |         |            |

|------|-------------|-----|-----|-----|----------|----------|---------|------------|

| 001  | 1100        | STP |     |     |          |          |         |            |

| 010  |             |     |     |     |          |          |         | <b>y</b> . |

| 011  | 5           | 5   |     |     |          | •        | O       |            |

| 100  | 1           | 0   |     |     |          |          |         |            |

| 101  | 5           | 5   |     |     |          | X        |         |            |

| 110  | 5           |     |     |     |          | 1        |         |            |

| 111  | 15          | 50  |     |     | V        | <b>)</b> |         |            |

| la a | 4 4t N1 -   | DO  | MAD | MDD | OID      | 100      | A 1 1 1 | 4040       |

| ins  | truction No | PC  | MAR | MDR | CIR      | ACC      | ALU     | 1010       |

|      |             |     |     | - 4 |          |          |         |            |

|      |             |     |     |     | <u> </u> |          |         |            |

|      |             |     |     |     |          |          |         |            |

|      |             |     |     | -0  |          |          |         |            |

|      |             |     | 4   | 0   |          |          |         |            |

|      |             |     | 0   |     |          |          |         |            |

|      |             |     | 20  |     |          |          |         |            |

|      |             |     |     |     |          |          |         |            |

|      |             |     | Y   |     |          |          |         |            |

|      |             |     |     |     |          |          |         |            |

|      | ••          |     | *   |     |          |          |         |            |

|      |             |     |     |     |          |          |         |            |

|      | -           |     |     |     |          |          |         |            |

|      |             |     |     |     |          |          |         |            |

|      |             |     |     |     |          |          |         |            |

|      |             |     |     |     |          |          |         |            |

|      |             |     |     |     |          |          |         |            |

|      |             |     |     |     |          |          |         |            |

|      |             |     |     |     |          |          |         |            |

|      |             |     |     |     |          |          |         |            |

|      |             |     |     |     |          |          |         |            |

| Practice Questions                                                                      |     |

|-----------------------------------------------------------------------------------------|-----|

| Q 4.5) Describe what differs a computer with a calculator                               |     |

|                                                                                         | [1] |

| <b>Q 4.6)</b> Differentiate an ALU with a calculator.                                   |     |

|                                                                                         |     |

| Q 4.7) Von Neumann gave the idea how computer should be built.                          |     |

| a) Describe the purpose of each of the following parts of a processor: (i) Control unit |     |

|                                                                                         | [1] |

| (ii) Arithmetic & Logic unit                                                            | )   |

|                                                                                         | [1] |

| (iii) Register                                                                          |     |

|                                                                                         |     |

| <b>b)</b> Draw and label the diagram of von Neumann architecture.                       |     |

Q 4.8) Draw the diagram and describe the stages of fetch-execute cycle.

Q 4.9) Description of fetch-execute cycle:

| [6]                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------|

| Q 4.10) The sequence of operations shows, in register transfer notation, the fetch stage of the                   |

| fetch-execute cycle.                                                                                              |

| 1 MAR←[PC]                                                                                                        |

| 2 PC ←[PC] + 1                                                                                                    |

| 3 MDR ←[[MAR]]                                                                                                    |

| 4 CIR ←[MDR]                                                                                                      |

| • [register] denotes contents of the specified register or memory location                                        |

| <ul> <li>step 1 above is read as "the contents of the Program Counter are copied to the Memory Address</li> </ul> |

| Register"                                                                                                         |

| (i) Describe what is happening at step 2.                                                                         |

| (4) I I I I I I I I I I I I I I I I I I I                                                                         |

|                                                                                                                   |

| (ii) Describe what is happening at step 3.                                                                        |

| (ii) Bessiles Marie Happering at step e.                                                                          |

| [1]                                                                                                               |

| (iii) Describe what is happening at step 4.                                                                       |

|                                                                                                                   |

|                                                                                                                   |

| Q 4.11) (a) Describe basic Von Neumann processor architecture.                                                    |

| 4.11) (a) Describe basic volt Neumann processor architecture.                                                     |

|                                                                                                                   |

|                                                                                                                   |

| [2]                                                                                                               |

| (h) At a particular part in a present the present accepted (DC) contains the value 200                            |

| (b) At a particular point in a program, the program counter (PC) contains the value 200.                          |

| (i) State the expected value contained in the PC after the instruction held at location 200 has been              |

| fetched                                                                                                           |

| Explain your answer.                                                                                              |

|                                                                                                                   |

| [1]                                                                                                               |

| Q 4.12) One of the buses found in a typical microprocessor architecture is the control bus.                       |

| Describe its purpose.                                                                                             |

| [1]                                                                                             |

|-------------------------------------------------------------------------------------------------|

| Q 4.13) (i) One of the buses found in a typical microprocessor architecture is the control bus. |

| Describe its purpose.                                                                           |

|                                                                                                 |

| [1]                                                                                             |

| Give <b>one</b> example of a control signal used.                                               |

| [1]                                                                                             |

| (ii) Name and describe two other buses used in a typical microprocessor architecture.           |

| 1                                                                                               |

| 2[2]                                                                                            |

|                                                                                                 |

| Q 4.14) (ii) The contents of some special-purpose registers change as the program is executed.  |

| Complete the trace table for the fetching of the first program instruction (867A):              |

| Show how the contents of the registers change.                                                  |

| • Put a tick in the address bus and/or data bus column to show when there is a signal change on |

|               |                         |           | -00      |        |         |      |  |

|---------------|-------------------------|-----------|----------|--------|---------|------|--|

|               | Sp                      | ecial pur | pose reg | isters | Buses   |      |  |

| Fetch stage   | (Contents shown in hex) |           |          | buses  |         |      |  |

| 1 otom stage  | DC                      | MAR       | MDB      | CIP    | Address | Data |  |

|               | PC                      | MAR       | MDR      | CIR    | bus     | bus  |  |

|               | 58                      |           |          |        |         |      |  |

| MAR ← [PC]    | 0                       |           |          |        |         |      |  |

| PC ← [PC] + 1 |                         |           |          |        |         |      |  |

| MDR ←[[MAR]]  |                         |           |          |        |         |      |  |

| CIR ← [MDR]   |                         |           |          |        |         |      |  |

each bus.

[5]

Q 4.17) The following text includes a description of four stages of the fetch-execute cycle. Use the

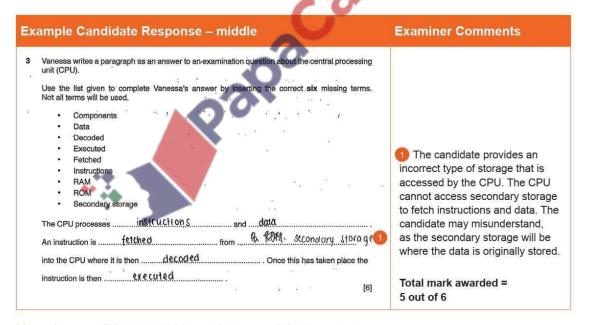

terms below to complete the text: Memory Data Register (MDR), Memory Address Register (MAR), Program Counter (PC), Current Instruction Register(CIR), address, data bus, main memory, address bus. The program instructions are stored in a continuous block of ...... Stage 1: The contents of the Program Counter are copied to incremented. Stage 3 The value in the Memory Address Register is loaded to the Memory Data Register are copied to the...... and. The instruction can now be decoded and executed. Summer 2019 P12 **3** Vanessa writes a paragraph as an answer to an examination question about the central processing unit (CPU). Use the list given to complete Vanessa's answer by inserting the correct six missing terms. Not all terms will be used. Decoded Components Fetche Instructions Executed · ROM RAM Secondary storage instruction is then .... [6]

# **Candidate Example response**

# Question 3

| Example Candidate Response – high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Examiner Comments                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Vanessa writes a paragraph as an answer to an examination question about the central processing unit (CPU).  Use the list given to complete Vanessa's answer by inserting the correct six missing terms. Not all terms will be used.  Components  Data  Decoded Executed Fetched Instructions RAM ROM Secondary storage  The CPU processes Allo and Instructions  An instruction is Letched from DAM into the CPU where it is then decoded Once this has taken place the instruction is then assessment of the control of the contro | 1 The candidate provides six correct terms, in the correct places.  Total mark awarded = 6 out of 6 |

# How the candidate could have improved their answer

The candidate provided a fully correct answer that could not have been improved.

# How the candidate could have improved their answer

The candidate demonstrated a good understanding of the central processing unit. However, it would have been beneficial if they had understood that the CPU would fetch instructions and data from the RAM and not secondary storage.

| Example Candidate Response – low                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Examiner Comments                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vanessa writes a paragraph as an answer to an examination question about the central processing unit (CPU).  Use the list given to complete Vanessa's answer by inserting the correct six missing terms. Not all terms will be used.  Components  Data  Decoded - Executed Fetched - Instructions RAM ROM Secondary storage  The CPU processes RAM and Rom An instruction is Fotched from Secondary to ray e into the CPU where it is then Decoded from Secondary of the instruction is then [6] | <ol> <li>The candidate shows misunderstanding of what the CPU processes. They provide two components from the computer, rather than items such as data and instructions.</li> <li>The candidate also misunderstands that the CPU is able to fetch data from secondary storage. It would be beneficial for the candidate to understand that the CPU can only access the RAM.</li> <li>Total mark awarded = 3 out of 6</li> </ol> |

# How the candidate could have improved their answer

The candidate misunderstood the CPU although they understood that it had a cycle that fetched, decoded and executed. They misunderstood what the CPU processed. They also showed the same misunderstanding that the CPU fetched data from secondary storage.

# Common mistakes candidates made in this question

Some candidates misunderstood that the CPU fetched data and instructions from secondary storage. They may have thought this, as the data may originally have been stored in the secondary storage, however, it would have been beneficial for candidates to have understood that the data needed to be brought into RAM, before it could be accessed by the CPU.

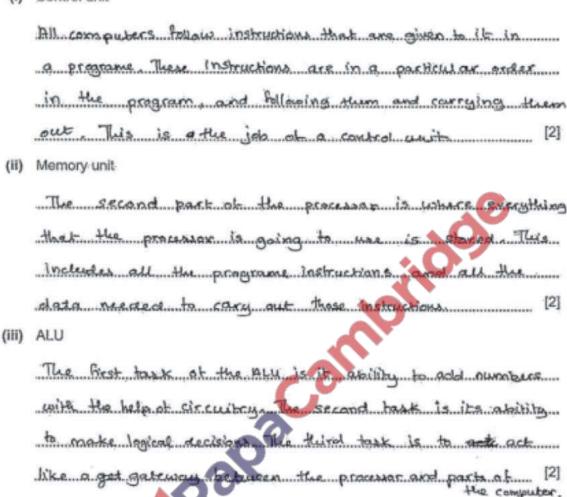

# Question 5 (a)

Describe the purpose of each of the following parts of a processor:

- (i) Control unit

- (ii) Memory unit

- (iii) ALU

### Mark scheme

- (i) Manages the execution of instructions

- Fetches each instruction in turn

- Decodes and synchronises its execution...

- by sending control signals to other parts of processor [2]

- (ii) Stores program in current use

- Stores data in current use

[2]

- Stores parts of OS in current use

- Carries out comparisons

(iii) - Carries out arithmetic operations

(1 per –, max 2 per dotty, max 6) [2]

- Acts as gateway in and out of processor

# Example candidate response – grade A

| (i)   | Control unit                                                                                                               |

|-------|----------------------------------------------------------------------------------------------------------------------------|

|       | Control unit is that pait of processor that instructs are                                                                  |

|       | the other components, what to do throw It fetches contract                                                                 |

|       | cine from the main minory and decoder them & and then                                                                      |

| (ii)  | it cause those the execution of those instructions [2] by the other components of the controlling with a clock Memory unit |

|       | Memory unit story instructions and darks that                                                                              |

|       | are being executed by the processor, It the processor,                                                                     |

|       | needs to access this date your it can access the                                                                           |

|       | them guickly from the man memory [2]                                                                                       |

| (iii) | ALU                                                                                                                        |

|       | ALU (Arithmete logic linit) contains circuit any to                                                                        |

|       | manipulate data of can perform lagical and arithmetic                                                                      |

|       | operations on data Fruthmore, all input and output                                                                         |

|       | duries must see though the ALV. [2]                                                                                        |

### **Examiner comment**

In part (i), the answer went way beyond what was necessary for full marks. They referred to the fetch cycle, execution of decoded instructions, reference to clock etc. More than enough for full marks. In part(ii), the candidate clearly understood that data and instructions (currently in use) are stored in the memory unit. This reference to currently in use distinguished grade A candidates from the grade C candidates, as seen in the example below. The third part was also clearly laid out – the ALU performs logical and arithmetic operations is very clear and unambiguous. Lower ability candidates tend to refer to doing some arithmetic and making logical decisions which indicates a lack of understanding of how the ALU works.

# Example candidate response - grade C

(i) Control unit

### **Examiner comment**

Part (i) was not really describing the control unit. Part (ii) did not mention that data and instructions currently in use are stored here. The third part was sketchy with the candidate describing the ALU as 'adding numbers' and 'making logical decisions'. The only part which was awarded a mark was the reference to the ALU acting as a *gateway*. Candidates at grade C tended to know the terms but were unclear of how it all interlinked and produced very vague, often incorrect, answers to questions of this type.

# Example candidate response - grade E

| (i)   | Control unit                                                        |

|-------|---------------------------------------------------------------------|

|       | It manages the processing.  It tetches the things done in polenting |

|       |                                                                     |

|       |                                                                     |

| (ii)  | Memory unit                                                         |

|       | It stores what the things in the while processing -                 |

|       | used next time. [2]                                                 |

| (iii) | Arthimatics are done in the ALU.                                    |

|       | All the calculations are done in the                                |

|       | [2]                                                                 |

# **Examiner comment**

The occasional correct word like *fetch* was used, but the candidate had no real understanding of how the control unit works. Part (ii) was a little better, with the candidate showing some idea of how the memory unit works but falls short of making some key comments which could gain marks. In part (iii), a reference to arithmetic and calculations was the level of understanding. There was no mention of arithmetic operations or logical comparisons in their answer.

(c) The table shows six stages in the von Neumann fetch-execute cycle.

Put the stages into the correct sequence by writing the numbers 1 to 6 in the right hand column.

| Description of stage                                                                                                                              | Sequence<br>number |

|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| the instruction is copied from the Memory Data Register (MDR) and placed in the Current Instruction Register (CIR)                                |                    |

| the instruction is executed                                                                                                                       |                    |

| the instruction is decoded                                                                                                                        |                    |

| the address contained in the Program Counter (PC) is copied to the Memory Address Register (MAR)                                                  |                    |

| the value in the Program Counter (PC) is incremented so that it points to the next instruction to be fetched                                      | 8                  |

| the instruction is copied from the memory location contained in the Memory Address Register (MAR) and is placed in the Memory Data Register (MDR) |                    |

[6]

# **Example Candidate Response High, Middle and Low**

| . Description of stage                                                                                                                               | Sequence<br>number |

|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| the instruction is copied from the Memory Data Register (MDR) and placed in the Current Instruction Register (CIR)                                   | 4                  |

| the instruction is executed                                                                                                                          | 6                  |

| the instruction is decoded                                                                                                                           | 5                  |

| the address contained in the Program Counter (PC) is copied to the Memory Address Register (MAR)                                                     | 1                  |

| the value in the Program Counter (PC) is incremented so that it points to the next instruction to be fetched.                                        | 2                  |

| the instruction is copied from the memory location contained in the Memory<br>Address Register (MAR) and is placed in the Memory Data Register (MDR) | 3                  |

[6]

# Examiner comment – high

In part (c), in common with the vast majority of candidates, this candidate has correctly identified the sequence of stages of the von Neumann fetch-execute cycle. Marks awarded in part (c) = 6/6

# **Topical Questions from Past Papers**

# Q 1) Summer 2015 P11

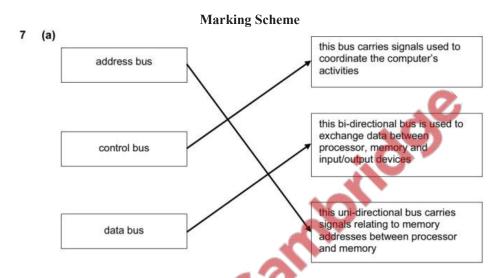

7 (a) One of the key features of von Neumann computer architecture is the use of buses. Three buses and three descriptions are shown below.

Draw a line to connect each bus to its correct description.

This bus carries signals used to coordinate the computer's activities

Control bus

This bi-directional bus is used to exchange data between processor, memory and input/ output devices

Data bus

This uni-directional bus carries signals relating to memory addresses between processor and memory

**(b)** The seven stages in a von Neumann fetch-execute cycle are shown in the table below. Put each stage in the correct sequence by writing the numbers 1 to 7 in the right hand column. The first one has been done for you.

| Stage                                                                          | Sequence number |

|--------------------------------------------------------------------------------|-----------------|

| the instruction is then copied from the memory location contained in the MAR   |                 |

| (memory address register) and is placed in the MDR (memory data register)      |                 |

| the instruction is finally decoded and is then executed                        |                 |

| the PC (program counter) contains the address of the next instruction to be    | 1               |

| fetched                                                                        |                 |

| the entire instruction is then copied from the MDR (memory data register) and  |                 |

| placed in the CIR (current instruction register)                               |                 |

| the address contained in the PC (program counter) is copied to the MAR         |                 |

| (memory address register) via the address bus                                  |                 |

| the address part of the instruction, if any, is placed in the MAR (memory      |                 |

| address register)                                                              |                 |

| the value in the PC (program counter) is then incremented so that it points to |                 |

| the next instruction to be fetched                                             |                 |

Examiner's Comments on Question 7 (a) and (b)

Part (a) was answered very well with most candidates able to gain two marks.

In part (b) very few candidates gained full marks despite the range of responses they could have given. Most candidates demonstrated a need to improve their knowledge of the fetch-execute cycle. Many candidates gained just one mark for the incrementation of the program counter. Some candidates gained three marks for identifying some correct stages.

# Q 2) Winter 2015 P13

**3** A section of computer memory is shown below:

| Content   |

|-----------|

| 0110 1110 |

| 0101 0001 |

| 1000 1101 |

| 1000 1100 |

|           |

|           |

|           |

|           |

|           |

|           |

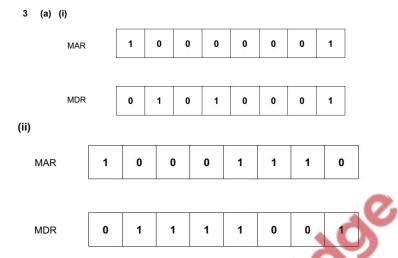

| (a) (i) The contents of mem | nory location 1000 0001 are to be read.                                                        |      |

|-----------------------------|------------------------------------------------------------------------------------------------|------|

|                             | Memory Address Register (MAR) and the Memory Data Register (M                                  | MDR) |

| during this read operation: | [2]                                                                                            |      |

| MAR                         |                                                                                                |      |

|                             |                                                                                                |      |

| MDR                         |                                                                                                |      |

|                             | s to be written into memory location 1000 1110.  MAR and MDR during this write operation:  [2] |      |

| MAR                         |                                                                                                |      |

|                             |                                                                                                |      |

| MDR                         |                                                                                                |      |

| •                           |                                                                                                |      |

(iii) Show any changes to the computer memory following the read and write operations in **part** (a)(i) and **part** (a)(ii). [1]

| Address   | Content   |

|-----------|-----------|

| 1000 0000 | 0110 1110 |

| 1000 0001 | 0101 0001 |

| 1000 0010 | 1000 1101 |

| 1000 0011 | 1000 1100 |

|           |           |

| 1000 1100 |           |

| 1000 1101 |           |

| 1000 1110 |           |

| 1000 1111 |           |

| (b) Name three other registers used in computers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 1<br>2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| (c) The control unit is part of a computer system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | [-]   |

| What is the function of the control unit?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |