# AS/A Level GCE

# **GCE Electronics**

OCR Advanced Subsidiary GCE in Electronics H065

OCR Advanced GCE in Electronics H465

version 5 – September 2013

© OCR 2013

# Contents

| 1 | Abo        | ut these Qualifications                                                                             | 4        |

|---|------------|-----------------------------------------------------------------------------------------------------|----------|

|   | 1.1        | The Three-Unit AS                                                                                   | 4        |

|   | 1.2        | The Six-Unit Advanced GCE                                                                           | 4        |

|   | 1.3        | Qualification Titles and Levels                                                                     | 4        |

|   | 1.4        | Aims                                                                                                | 5        |

|   | 1.5        | Prior Learning/Attainment                                                                           | 5        |

| 2 | Sum        | nmary of Content                                                                                    | 6        |

| _ | Juli       | iniary of Content                                                                                   | U        |

|   | 2.1        | AS Units                                                                                            | 6        |

|   | 2.2        | A2 Units                                                                                            | 7        |

| 3 | Unit       | : Content                                                                                           | 8        |

|   |            |                                                                                                     |          |

|   | 3.1        | AS Unit F611: Simple Systems                                                                        | 8        |

|   | 3.2        | AS Unit F612: Signal Processors                                                                     | 14       |

|   | 3.3        | AS Unit F613: Build and Investigate Electronic Circuits                                             | 18<br>21 |

|   | 3.4<br>3.5 | A2 Unit F614: Electronic Control Systems A2 Unit F615: Communication Systems                        | 26       |

|   | 3.6        | A2 Unit F615: Communication Systems A2 Unit F616: Design, Build and Investigate Electronic Circuits | 32       |

|   | 0.0        | 72 Office Office Design, Dana and investigate Electronic Officials                                  |          |

| 4 | Sch        | emes of Assessment                                                                                  | 34       |

|   | 4.1        | AS GCE Scheme of Assessment                                                                         | 34       |

|   | 4.2        | Advanced GCE Scheme of Assessment                                                                   | 35       |

|   | 4.3        | Unit Order                                                                                          | 36       |

|   | 4.4        | Unit Options (at AS/A2)                                                                             | 36       |

|   | 4.5        | Synoptic Assessment (A Level GCE)                                                                   | 36       |

|   | 4.6        | Assessment Availability                                                                             | 36       |

|   | 4.7        | Assessment Objectives                                                                               | 37       |

|   | 4.8        | Quality of Written Communication                                                                    | 38       |

| 5 | Tecl       | hnical Information                                                                                  | 39       |

|   | 5.1        | Making Unit Entries                                                                                 | 39       |

|   | 5.2        | Making Qualification Entries                                                                        | 40       |

|   | 5.3        | Grading                                                                                             | 40       |

|   | 5.4        | Result Enquiries and Appeals                                                                        | 41       |

|   | 5.5        | Shelf-Life of Units                                                                                 | 41       |

|   | 5.6        | Unit and Qualification Re-sits                                                                      | 41       |

|   | 5.7        | Guided Learning Hours                                                                               | 41       |

|   | 5.8        | Code of Practice/Subject Criteria/Common Criteria Requirements                                      | 42       |

|   | 5.9        | Arrangements for Candidates with Particular Requirements                                            | 42       |

|   | 5.10       | Prohibited Qualifications and Classification Code                                                   | 42       |

|   | 5.11       | Coursework Administration/Regulations                                                               | 43       |

| 6 | Oth        | er Specification Issues                                                                             | 44       |

|   | 6.1        | Overlap with other Qualifications                                                                   | 44       |

|   | 6.2        | Progression from these Qualifications                                                               | 44       |

|   | 6.3        | Key Skills Mapping                                                                                  | 44       |

|   |            |                                                                                                     |          |

|                                                                                                         | 6.4   | Spiritual, Moral, Ethical, Social, Legislative, Economic and Cultural Issues                                      | 45      |  |

|---------------------------------------------------------------------------------------------------------|-------|-------------------------------------------------------------------------------------------------------------------|---------|--|

|                                                                                                         | 6.5   | Sustainable Development, Health and Safety Considerations and European Developments                               | 45      |  |

|                                                                                                         | 6.6   | Avoidance of Bias                                                                                                 | 45      |  |

|                                                                                                         | 6.7   | Language                                                                                                          | 45      |  |

|                                                                                                         | 6.8   | Disability Discrimination Act Information Relating to these Specifications                                        | 46      |  |

|                                                                                                         |       |                                                                                                                   |         |  |

| App                                                                                                     | endix | A: Performance Descriptions                                                                                       | 47      |  |

|                                                                                                         |       | B: Coursework Assessment Criteria for AS Unit F613: Build and te Electronic Circuits                              | 50      |  |

| Appendix C: Suggested Investigations for AS Unit F613: <i>Build and Investigate Electronic Circuits</i> |       |                                                                                                                   |         |  |

|                                                                                                         |       | D: Investigation Assessment Criteria for A2 Unit F616: <i>Design, Build and</i><br>te <i>Electronic Circuit</i> s | d<br>55 |  |

|                                                                                                         |       | E: Suggested Investigations for A2 Unit F616: <i>Design, Build and</i> te <i>Electronic Circuits</i>              | 58      |  |

| App                                                                                                     | endix | F: Formulae Relationships and Boolean Algebra                                                                     | 59      |  |

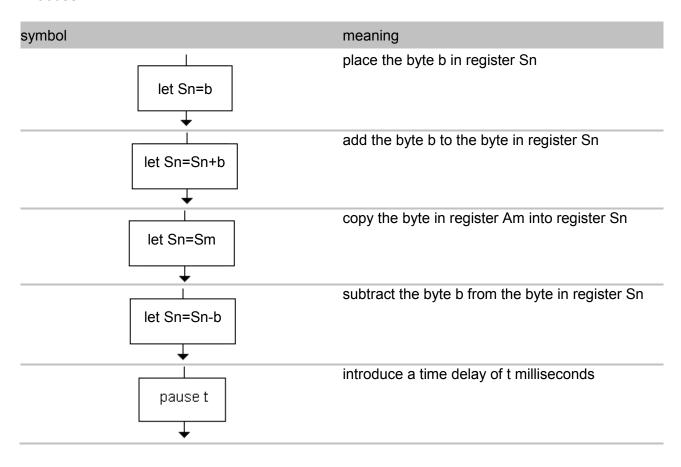

| App                                                                                                     | endix | G: Microcontroller flowchart symbols                                                                              | 61      |  |

| Арр                                                                                                     | endix | H: Assembler Codes                                                                                                | 63      |  |

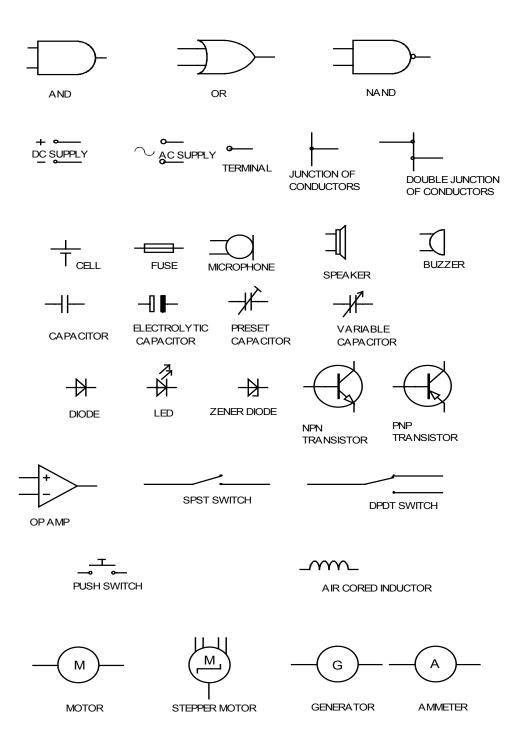

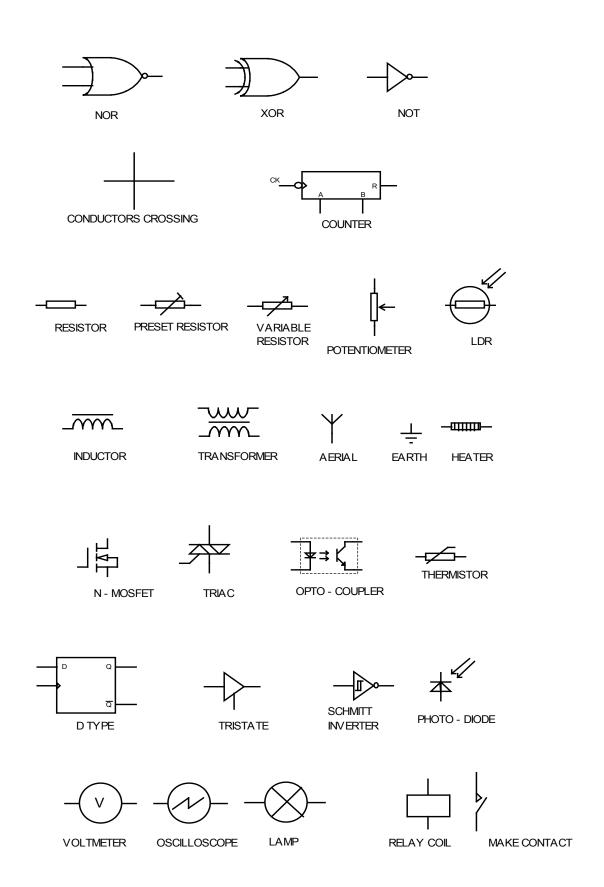

| Арр                                                                                                     | endix | I: Standard Circuit Symbols                                                                                       | 64      |  |

| App                                                                                                     | endix | J: Guidance for the production of electronic coursework moderation                                                | 66      |  |

Vertical black lines indicate a significant change to the previous printed version.

# 1 About these Qualifications

This booklet contains OCR's Advanced Subsidiary (AS) GCE and Advanced GCE specifications in electronics for teaching from September 2013.

These AS GCE and Advanced GCE specifications aim to provide an introduction to and thorough grounding in electronics. They are designed around a systems approach to electronics that introduces a wide range of transducers and input, output and processing systems and encourages a practical, problem-solving approach. Project work allows the development of skills and the application of knowledge in the solution of a practical problem. The specifications aim to give an introduction to the electronics involved in modern communication and control systems.

# 1.1 The Three-Unit AS

The Advanced Subsidiary GCE is both a 'stand-alone' qualification and also the first half of the corresponding Advanced GCE. The AS GCE is assessed at a standard appropriate for candidates who have completed the first year of study (both in terms of teaching time and content) of the corresponding two-year Advanced GCE course, ie between GCSE and Advanced GCE.

From September 2013 The AS GCE is made up of **three** mandatory units, of which **two** are externally assessed and **one** is internally assessed. These units form 50% of the corresponding six-unit Advanced GCE.

# 1.2 The Six-Unit Advanced GCE

From September 2013 The Advanced GCE is made up of **three** mandatory units at AS and **three** further units at A2. **Two** A2 units are externally assessed and **one** A2 unit is internally assessed.

# 1.3 Qualification Titles and Levels

These qualifications are shown on a certificate as:

- OCR Advanced Subsidiary GCE in Electronics.

- OCR Advanced GCE in Electronics.

Both qualifications are Level 3 in the National Qualification Framework (NQF).

## 1.4 Aims

The aims of these specifications are to:

- develop and sustain an interest in and an enjoyment of electronics and its applications;

- develop an awareness and an understanding of the social and economic implications of electronics;

- develop knowledge and understanding of the principles of electronics that are desirable in a technologically-based society;

- develop an appropriate body of knowledge for those not studying the subject beyond this stage, which will also serve as a foundation for more advanced studies in electronics;

- develop the skills of observation, experimentation and the processing and interpretation of data;

- apply qualitatively and quantitatively their knowledge and understanding of electronic principles;

- apply a logical approach to the analysis and synthesis of complex systems;

- develop the practical skills associated with the design, construction and testing of electronic systems;

- foster relevant communication skills.

# 1.5 Prior Learning/Attainment

No prior knowledge of the subject is required. The specifications build on, but do not depend on, the knowledge, understanding and skills specified for GCSE Electronics. It is recommended that candidates have attained communication and literacy skills at a level equivalent to GCSE Grade C in English.

The specifications have been written without assuming that candidates will be taking A Level Mathematics or Physics in conjunction with the course. However, prior acquaintance with relevant parts of GCSE Mathematics and Science specifications would be an advantage. It is assumed that any tuition needed to cope with the mathematics implied by the specifications would be provided to supplement the basic teaching of the specifications.

# 2 Summary of Content

# 2.1 AS Units

# Unit F611: Simple Systems

- Simple Digital Systems

- Digital from Analogue

- Pulses

- Logic Systems

# Unit F612: Signal Processors

- Storing signals

- Negative feedback

- Counting pulses

- Amplifying audio

- Microcontrollers

# Unit F613: Build and Investigate Electronic Circuits

#### Three short tasks:

- · a digital circuit;

- an analogue circuit that uses an op-amp;

- a microcontroller circuit in which the microcontroller has been programmed using a flowchart technique.

# 2.2 A2 Units

# Unit F614: Electronic Control Systems

- MOSFET Circuits

- Digital Processing

- Servo Control

- Microcontroller Systems

# Unit F615: Communication Systems

- Video Displays

- Modulating Carriers

- Frequency Division Multiplexing

- Time Division Multiplexing

# Unit F616: Design, Build and Investigate Electronic Circuits

A single project in which candidates design, build, test and analyse a circuit that serves a

useful purpose

# 3 Unit Content

# 3.1 AS Unit F611: Simple Systems

This unit introduces candidates to the fundamentals of modern electronics.

This includes the use of:

- basic equations to calculate quantities;

- standard prefixes and units to state values of quantities;

- standard circuit symbols in circuit diagrams;

- measuring instruments;

- models for voltage, current and power in circuits;

- block diagrams to analyse circuits;

- passive and active components to generate, process and display signals;

- truth tables, Boolean algebra and graphs to represent the transfer characteristics of components and systems.

#### It is recommended that candidates are familiar with the following areas.

Candidates should know and understand:

- the concepts of conductors and insulators in terms of the mobility of charge;

- voltage as a measure of the energy per charge at a point in a circuit;

- current as the rate of transfer of charge past a point in a circuit;

- need for a power supply to maintain a current in a circuit;

- the conversion of energy from electrical to other forms as charge moves round a circuit;

- the behaviour of currents at a junction;

- the voltage across a series circuit is the sum of the voltage across the components;

- the current in a series circuit is the same in all the components.

## 1.1 Simple Digital Systems

Switches in series with resistors can be used to convert information into digital signals.

Candidates should be able to:

- (a) recall how to use switches and pull-up or pulldown resistors in series with a power supply to generate digital signals;

- (b) recall that, unless otherwise stated, logic 1 (high) is a signal at +5 V and logic 0 (low) is a signal at 0 V;

- (c) recall and use the defining equation for resistance ( $R = \frac{V}{I}$ );

- (d) recall and use the equation for power( P = VI ) to calculate the rate of heating, or output power, of a component;

- (e) recall that components have maximum ratings for current, voltage or power;

- (f) recall how to use multimeters as voltmeters, ammeters and ohmmeters to measure voltage, current and resistance in a circuit;

- (g) understand the use of the prefixes G, M, k, m,  $\mu$ , n and p when calculating values of quantities.

Digital signals can be processed by logic gates.

- (h) recall the transfer characteristic of a NOT gate (an input above +3 V gives 0 V at the output, an input below +2 V gives +5 V at the output), and represent it as an input—output graph;

- (i) recall the truth tables of the following twoinput logic gates: AND, EOR, NAND, NOR, OR;

- understand the use of an LED to indicate the state of a logic gate's output (including the need for a series resistor);

- (k) recall the transfer characteristic of an LED and represent it as a current–voltage graph (no current in reverse bias; current rises rapidly in forward bias when voltage reaches 2 V).

A logic gate's output signal can be used to switch a variety of devices on and off via a driver.

#### Candidates should be able to:

- (a) recall that logic gates can only source or sink currents of a few milliamps, so cannot supply much power to output devices:

- (b) understand that a MOSFET is a voltage-controlled resistor (the voltage at the gate determines the resistance between the drain and the source);

- (c) recall the transfer characteristic of a MOSFET (drain-source resistance is infinite until gate-source voltage reaches a threshold value, then drops to a constant low value for higher gatesource voltages) and represent it as a resistance-voltage graph.

- (d) recall that MOSFETS with appropriate threshold voltages can act as drivers, sinking current from motors, heaters, buzzers and lamps.

Standard symbols are used. to draw circuit diagrams.

The flow of information through a system can be shown with block diagrams.

- (e) recall and use standard circuit symbols to draw circuit diagrams;

- understand that circuit diagrams omit power supply connections for integrated circuits;

- (g) represent a simple digital system as a block diagram, showing input, processing and output stages;

- (h) understand that a block diagram shows the flow of information through a system;

- understand that block diagrams make it easier to analyse the operation of a system;

- (j) analyse and synthesise circuit and block diagrams for digital systems with only one logic gate

#### 1.2 Digital from Analogue

The resistance of some components depends on their environment. They can be used as sensors. Candidates should be able to:

- (a) recall the transfer characteristic of an LDR (resistance falls as light intensity increases) and represent this as a resistance—intensity graph;

- (b) recall the transfer characteristic of a thermistor (resistance falls as temperature increases) and represent this as a resistance–temperature graph;

- (c) recall and use the equation for the resistance of resistors in series  $(R = R_1 + R_2)$  and parallel;

- (d) calculate the output voltage of an unloaded voltage divider made from a pair of resistors in series with a power supply;

- (e) understand the use of a potentiometer to generate a signal of variable voltage;

- (f) understand the difference between analogue and digital signals (analogue have any value, digital have just two).

Op-amps can convert the analogue signal from a sensor into a digital signal for a logic system.

- (g) recall the transfer characteristic of an open-loop op-amp operating from supply rails at +15 V and -15 V (output saturates at +13 V if non-inverting input higher than inverting input, otherwise output saturates at -13 V);

- (h) understand that an ideal op-amp can be modelled as having no current at its inputs, but able to source or sink currents of up to 10 mA;

- understand the use of a diode in series with resistors to convert the output of an op-amp into high and low signals for a logic system;

- recall the transfer characteristic for a diode and represent it as a current–voltage graph (no current in reverse bias; current rises rapidly in forward bias when voltage reaches 0.7 V);

- (k) understand the use of a zener diode in series with a resistor to generate a fixed voltage at one of the inputs of an op-amp;

- recall the transfer characteristic for a zener diode and represent it as a current-voltage graph (no current in reverse bias until the breakdown voltage; current rises rapidly in forward bias when voltage reaches 0.7 V);

- (m) analyse and synthesise sensor systems with digital outputs for position, light intensity and temperature.

Capacitors can delay the change of a signal.

Candidates should be able to:

- (n) recall the exponential change in voltage across a capacitor as it is charged or discharged from a constant voltage through a resistor, and represent it as a voltage—time graph;

- (o) recall and use the equation for time constant  $(\tau = RC)$ ;

- (p) recall and use the idea that the voltage across the resistor of an RC series circuit is halved in a time of  $0.7\tau$ :

- (q) understand the use of a capacitor to delay the change of signal caused by the closing or opening of a switch in series with a resistor.

## 1.3 Pulses

A monostable uses an RC network to generate a single pulse.

- (a) understand the use of an RC network to generate spikes from rising or falling edges, representing them as voltage—time graphs at input and output (exponential drop lasts about two time constants);

- (b) understand the use of diodes as clamps to suppress spikes from RC networks;

- (c) understand the use of a pair of NAND gates and an RC network to make a monostable the output of which goes low for 0.7 RC s when triggered by a falling edge;

- (d) recall that inputs to logic gates draw no current and have clamping diodes to the supply rails;

- (e) sketch voltage—time graphs at inputs and outputs of the logic gates in a monostable.

A relaxation oscillator uses a Schmitt trigger NOT gate to produce a continuous train of pulses.

Candidates should be able to:

- recall the transfer characteristic of a Schmitt trigger NOT gate and represent it as an input-output graph (no recall of trip point values required);

- (g) understand the use of an RC network and Schmitt trigger NOT gate to make an oscillator and sketch voltage-time graphs at input and output (period T = 0.5RC);

- (h) understand how to use an oscilloscope to observe voltages that vary with time (including use of timebase and vertical amplifier settings to measure amplitude and period);

- (i) recall and use the equation for frequency

- understand the use of a driver to provide the interface between an oscillator and a loudspeaker.

## 1.4 Logic Systems

Combinations of logic gates can process signals Candidates should be able to: in many different ways.

- (a) understand the use of truth tables to analyse the behaviour of logic systems with up to three inputs;

- (b) recall and use Boolean algebra to represent the output of logic gates;

- (c) recall and use Boolean algebra to represent the output columns of a truth table;

- (d) understand the construction of a truth table from a Boolean algebra expression;

- (e) understand the use of Boolean algebra to represent the behaviour of a logic system (including the use of the rules given in Appendix B to simplify expressions);

- (f) synthesise AND, OR and NOT gates from NAND gates;

- (g) understand the use of NAND gates to synthesise logic systems with up to four

- (h) understand the advantages of only using NAND gates (more economic use of integrated circuits, economies of scale);

- analyse the behaviour of logic systems with up to four inputs and four outputs.

# 3.2 AS Unit F612: Signal Processors

This module introduces candidates to systems that process signals through a series of subsystems. This includes the use of:

- bistables, latches and flip-flops to store digital information;

- op-amps as voltage, power and summing amplifiers to process audio frequency signals;

- counters to record pulses and generate sequences of digital signals;

- · microcontrollers as programmable devices.

#### **Recommended Prior Knowledge**

Candidates should have studied Unit F611 (Simple Systems).

## 2.1 Storing Signals

Arrays of logic gates can be used to store information.

- (a) recall the behaviour of a bistable (separate inputs to set and reset a single output) and represent its behaviour with timing diagrams;

- (b) understand the use of NOR gates to make a bistable with active high inputs;

- (c) understand the use of NAND gates to make a bistable with active–low inputs;

- (d) recall the behaviour of a latch (data and enable inputs to set and reset a single output) and represent its behaviour with timing diagrams;

- (e) analyse the operation of a latch made from logic gates and a bistable;

- (f) recall the behaviour of a rising-edge triggered D flip-flop (data, clock, set and reset inputs, complementary outputs) and represent its behaviour with timing diagrams;

- (g) analyse the operation of a D flip-flop made from a master–slave pair of latches;

- (h) understand the use of an array of D flip-flops to store a binary word.

## 2.2 Negative Feedback

Negative feedback allows op-amps to process audio signals.

Candidates should be able to:

- (a) recall the use of an electret microphone to transfer sounds into electrical signals, to include the use of a pull-up resistor and a coupling capacitor;

- (b) understand that an ideal amplifier increases the amplitude of an ac signal without altering its frequency or shape;

- (c) recall and use the equation for voltage gain  $(G = \frac{V_{out}}{V_{in}});$

- (d) recall that an op-amp is a differential amplifier  $(V_{\text{out}} = A(V_+ V_-))$  with a very large openloop gain A;

- (e) understand the use of negative feedback to make an op-amp into a voltage follower, including the need for a pull-down resistor at the non-inverting input;

- understand that a voltage follower has a voltage gain of one but can provide power gain.

Resistors can be used to make op-amps into non-inverting, inverting and summing amplifiers.

Candidates should be able to:

- (g) understand the use of feedback and pulldown resistors to make an op-amp into an non-inverting amplifier with a known voltage gain ( $G = 1 + \frac{R_f}{R_d}$ );

- (h) understand the use of feedback and input resistors to make an op-amp into an inverting amplifier with a known voltage gain  $(G = -\frac{R_f}{R_{in}}), \text{ to include the concept of virtual}$

earth for the inverting input;

- recall the transfer characteristics of inverting and non-inverting amplifiers based on op-amps, and represent them as input output graphs, including saturation;

- (j) understand the use of feedback and input resistors to allow an op-amp to combine two or more different ac signals

$$(-\frac{V_{out}}{R_f} = \frac{V_1}{R_1} + \frac{V_2}{R_2}...);$$

(k) recall that resistors in op-amp amplifiers need to be in the range 1 k $\Omega$  to 10 M $\Omega$ .

## 2.3 Counting Pulses

Arrays of D flip-flops can count pulses.

Candidates should be able to:

- (a) understand the connection of D to  $\overline{Q}$  to make a D flip-flop into a one-bit counter;

- (b) understand the use of D flip-flops and a NOT gate to make a binary ripple up-counter;

- (c) understand the use of logic gates to make binary counters that reset to *m* after *n* counts, where *m* and *n* are integers.

- (d) recall and use timing diagrams to represent the transfer characteristics of a binary counter;

- (e) recall the use of decoders and sevensegment LEDs to display the output of a binary counter in decimal.

Binary counters are at the heart of systems that produce sequences of digital signals.

Candidates should be able to:

- (f) understand the use of binary counters to make systems that can be used as clocks, including the use of crystal oscillators for precision timing;

- (g) understand the use of oscillators, logic systems and binary counters to generate continuous sequences of digital signals, to include frequency division;

- (h) understand the use of a flip-flop, oscillators, logic systems and binary counters to generate a single train of pulses when triggered by a pulse.

## 2.4 Amplifying Audio

An audio amplifier allows signals from a microphone to be heard from a loudspeaker.

- (a) explain the operation of a complete audio amplifier system in terms of blocks representing voltage amplifier, volume and tone controls and power amplifier;

- (b) recall and use the concepts of output and input impedance to solve problems of power and signal transfer between subsystems;

- (c) understand the use of a potentiometer as a volume control.

Capacitors can be used as filters.

Candidates should be able to:

- (d) explain the use of a capacitor as a frequency-dependant impedance, with impedance decreasing with increasing frequency;

- (e) recall and use the equation for break frequency  $(f_0 = \frac{1}{2\pi RC})$  in bass cut and treble cut filters:

- (f) recall the transfer characteristics of simple passive filters and represent them with loglog gain-frequency graphs, using straight line approximations;

- (g) understand treble cut, bass cut and bandpass filters based on op-amps, including the use of log-log gain-frequency graphs to represent their transfer characteristics.

#### 2.5 Microcontrollers

The behaviour of a microcontroller is fixed by the program fed into it.

Candidates should be able to:

- (a) describe a microcontroller as a digital system whose transfer characteristics are decided by the program stored in its memory;

- (b) understand the difference between hardware and the software that controls it:

- (c) understand the advantages of programmable systems (economies of scale, reusable, ease of system design);

- (d) understand the limitations of programmable systems (digital only, relatively slow);

- (e) understand the need for a host computer to translate a program into machine code and download it into a microcontroller.

A small set of microcontroller instructions allows Candidates should be able to: a wide range of behaviours.

- (f) understand the meaning of the terms input port, output port, memory address and register in the context of a microcontroller system;

- (g) understand that an analogue-to-digital converter outputs a byte that represents the input voltage;

- (h) recall and use flowcharts to analyse and design simple programs for microcontrollers, using the symbols of Appendix C;

- understand the use of hexadecimal notation to summarise four-bit binary words and bytes.

# 3.3 AS Unit F613: Build and Investigate Electronic Circuits

At AS Level, the investigation requirement consists of three separate circuits that candidates investigate by performing a single design, build, test and analyse cycle. Candidates also write a short report for each circuit investigated. The time spent on each circuit investigation is expected to be between 10 and 12 hours of laboratory time. The reports of the investigations should be between 500 and 1000 words for each investigation. Each circuit to be investigated will be a circuit taken from the three main elements of the AS specification, namely, a digital circuit, an analogue circuit and a microcontroller-based circuit. The work is marked by the centre and moderated by OCR.

#### Rationale

This new format will help candidates at AS Level to fully appreciate the cycle of design – build – test – analyse, as applied to an electronic circuit. Whether or not the candidate intends to continue electronics to A2 Level, all candidates at AS Level should develop these skills. The candidate will design and build an electronic circuit, and implement a test procedure that will allow a purposeful and reasoned analysis of the merits of the particular circuit characteristics. Candidates who choose to continue to A2 Level will then possess the skills required to successfully complete the requirements of the A2 investigation. The A2 investigation is a single project designed and built by the candidate. The coursework requirements at AS Level will focus the candidate on the design – build – test – analyse cycle applied to each subsystem, these skills will then be used in the complete A2 project.

#### Requirements

The three circuits to be considered must be one each from the following categories:

- A digital circuit

- An analogue circuit that uses an op-amp

- A microcontroller circuit in which the microcontroller has been programmed using a flowchart technique

The design of the digital and analogue circuits is not expected to be done by the candidates; it should be a circuit taken from class notes that will allow the candidate full access to the marks available (see Appendix B). It must be impressed upon candidates that these two investigations have, as the main focus, the build – test – analyse cycle. High marks can only be achieved if candidates carry out a well-planned and executed build – test – analyse cycle, and then produce a clear, concise report that details all aspects of the investigation and provides evidence of how test results were obtained. Centres are reminded that both the digital circuit and the op-amp circuit require at least one time-dependent input.

#### The digital circuit

The digital circuit must have, as a minimum requirement, at least one time-dependent input signal. Candidates choose an appropriate circuit encountered in the AS specification that will be within the means of the individual candidate, and also enable access to the full range of marks available, as shown in the assessment criteria found in Appendix B. Suggested circuits indicating the expected requirement are listed in Appendix C.

If candidates wish to investigate a digital circuit that is not considered in the AS specification but still meets the investigation requirements, it will be necessary for teachers to advise candidates on the suitability of the circuit.

The assessment criteria for this investigation are to be found in Appendix B.

### The analogue circuit

The analogue circuit must use an op-amp as the processing device. This circuit must contain, as a minimum requirement, at least one time-dependent input signal. It is intended that candidates choose an appropriate circuit encountered in the AS specification that will be within the means of the individual candidate, and also enable access to the full range of marks available, as shown in the assessment criteria found in Appendix B. Suggested circuits indicating the expected requirement are listed in Appendix C.

If candidates wish to investigate an op-amp based circuit that is not considered in the AS specification but still meets the investigation requirements, it will be necessary for teachers to advise candidates on the suitability of the circuit.

The assessment criteria for both investigations are identical and are to be found in Appendix B.

#### The microcontroller circuit

The microcontroller circuit must contain a microcontroller that has been programmed using a flowchart technique. Many centres will already be equipped to design and build microcontroller circuits using commonly available microcontrollers, for example, Microchip's PIC range of microcontrollers and Atmel's range of AVR microcontrollers. Many candidates will have already met the flowchart technique and this investigation is simply an extension of that process. However, those candidates who have not yet met the technique will not be disadvantaged as the flowchart technique to program microcontrollers is an integral part of the AS specification.

The circuit must contain at least two inputs, one of which is a time-dependent signal, and use, as a minimum requirement, two output pins. Centres are strongly advised to study the suggested microcontroller circuits detailed in Appendix C to appreciate the required level of the circuit.

The main focus of this investigation is the design – build – test – analyse cycle that has a small element of design introduced. High marks can only be achieved if candidates carry out a well-planned and executed design – build – test – analyse cycle, and then produce a clear, concise report that details all aspects of the investigation, including the evidence of how the test results were achieved.

There are currently a number of good flowcharting programs available, most of them being free to use. All flowcharting programs use the same symbols within the flowchart, and those used in this specification are detailed in Appendix G.

The assessment criteria for this investigation are to be found in Appendix B.

#### **General requirements**

All circuits should be built on prototype board/breadboard so that the circuit build can be assessed. No circuit should be built on PCB or built using a modular kit, as the circuit build forms part of the assessment criteria. It is not expected that candidates work with a circuit that involves mains voltage.

#### The investigation

For the digital and analogue investigation, all candidates are expected to plan and carry out a single build – test – analyse cycle. For the microcontroller circuit, candidates are expected to plan and carry out a single design – build – test – analyse cycle.

Candidates should keep a brief logbook/diary of the circuit investigation; this should include a record of all tests carried out. Candidates must be able to use the teacher as a resource, just like they would a book, webpage, etc. Where specific help is needed by the candidate in order to make progress with the investigation, it is the responsibility of the teacher to note this in the logbook/diary. The logbook/diary should be retained by the centre and made available if requested by the moderator.

The report Candidates are expected to write a concise report for each circuit investigation. The report is expected to be between 500 to 1000 words and must contain an A4 size colour photograph of the circuit build that clearly shows the quality of wiring and component placement. Marks are awarded for the quality of the circuit build. The report should detail clearly and succinctly all aspects of the investigation, including relevant and clear diagrams, and should be written in a style that is easy to read. Since emphasis is placed on the build – test – analyse cycle, candidates are advised to plan this carefully and ensure that the report contains detailed evidence of the cycle.

#### **Assessment**

The teacher assesses the investigation under four headings:

- Introduction and Planning

- The Circuit Build

- Testing and Analysis

- The Report

These four headings have been presented as the logical way in which an investigation would be conducted and are designed to aid the marking process.

The teacher marks the report and annotates the report clearly by indicating where it is felt particular criterion have been achieved. A simple mark in red ink is sufficient to highlight the evidence for the mark awarded with a reference to the particular criterion. It is important to annotate the reports in such a manner as this aids both the teacher and the moderator in identifying the evidence for particular marks awarded.

#### Moderation and internal standardisation

It is the responsibility of the centre to carry out internal standardisation where two or more teachers are responsible for the assessment. A single reliable order of merit must be produced.

Circuits should not be dismantled until the colour photograph has been taken and all assessment and, if necessary, internal standardisation has been carried out. Marks are then transferred to form MS1 and sent to OCR by the required date. Postal moderation then takes place according to OCR procedures.

For centres with ten or fewer candidates, all reports, along with the relevant part of form MS1, should be sent to the moderator by the specified date. For those centres with more than ten candidates, the relevant part of form MS1 only is sent in the first place to the moderator by the specified date. Upon receipt of this, the moderator will contact the centre and request a moderation sample.

# 3.4 A2 Unit F614: Electronic Control Systems

This unit introduces candidates to the use of analogue and digital electronic systems for control. This includes the use of:

- MOSFETs as variable resistors and amplifiers;

- processing and storing digital data;

- negative feedback to control a variety of physical quantities;

- microcontroller systems.

#### 4.1 MOSFET Circuits

MOSFETs are used to make a wide range of useful circuits.

- (a) recall the transfer characteristics of an nchannel MOSFET, representing them as graphs of drain current against gate-source voltage and drain current against drainsource voltage (including the use of threshold voltage and transconductance);

- (b) understand the use of a MOSFET as a voltage-controlled resistor for small drainsource voltages;

- understand the use of MOSFETs in a voltage divider circuit to make a potentiometer whose wiper position is controlled by an external voltage;

- (d) understand the use of MOSFETs in analogue switches, multiplexers and tristates;

- (e) understand the use of MOSFETs as voltage followers with very high input impedance (including the use of coupling capacitors to inject and extract signals);

- (f) understand the use of MOSFETs as high input impedance voltage amplifiers, including the need for biasing with a voltage divider to place the drain at a suitable voltage;

- (g) recall and use the equation for voltage gain  $(G = -g_m R_d)$  of a MOSFET amplifier;

- (h) recall the use of drain bias for a MOSFET amplifier (including why this is better than biasing with a voltage divider).

## 4.2 Digital Processing

Memory stores information as binary words.

Candidates should be able to:

- (a) recall the block diagram for a memory module (to include data bus, address bus and control bus);

- (b) understand that memory module stores information as binary words (one bit per cell), including how the number of data lines is related to the word length;

- (c) recall the relationship between the number of address lines and the number of different locations in the memory module;

- (d) understand that the control bus contains active-low read, write and enable lines;

- (e) recall the sequence of operations required for a word to be written to, and read from a location in a memory module.

Some types of memory can retain information in Candidates should be able to: the absence of a power supply.

- (f) recall the distinction between volatile and non-volatile memory;

- (g) understand the use of a D flip-flop and a tristate to make a volatile memory cell:

- (h) understand the use of a capacitor and a MOSFET to make a non-volatile memory cell;

- (i) understand the use of tristates to allow more than one memory module to access a common data bus;

- (j) understand the use of multiplexers and logic gates to combine small memory modules into large ones.

Digital information can be processed with registers and logic gates.

- (k) recall the use of D flip-flops to assemble registers;

- understand the use of registers and logic systems (such as full adders) in the parallel processing of pairs of binary words;

- (m) recall the use of two's complement coding to represent decimal numbers in binary code;

- (n) recall the use of AND and EOR gates to combine pairs of binary words stored in shift registers.

#### 4.3 Servo Control

Simple control systems use negative feedback.

Candidates should be able to:

- (a) understand the difference between open- and closed-loop control systems;

- (b) understand the operation of on-off servo control systems in terms of the following blocks: sensor, reference, comparator, switch, transducer;

- understand circuits for the on-off control of temperature, position, motor speed and light intensity (based on components studied at AS);

- (d) understand the use of voltage-time graphs to represent the response of an on-off control system to changes of conditions;

- (e) recall that on-off control results in a rapid response to change, but that the output never settles to a constant value.

Proportional control systems allow accurate control of a transducer.

Candidates should be able to:

- (f) understand the operation of proportional servo control systems in terms of the following blocks: sensor, reference, difference amplifier, voltage amplifier, ramp generator, power amplifier, transducer;

- (g) understand the use of an op-amp and four identical resistors to make a difference amplifier;

- (h) understand the use of an op-amp to make a ramp generator, including the use of the equation  $\Delta V_{out} = -V_{in} \frac{\Delta t}{RC}$ ;

- (i) understand the use of voltage-time graphs to represent the response of a proportional control system to changes of conditions;

- recall that proportional control systems respond relatively slowly, but allow the sensor and reference to settle at the same value.

Many power supplies use negative feedback to control the voltage at their output.

- (k) understand the use of a diode bridge and a capacitor to produce an unstabilised dc voltage from an ac supply;

- (I) understand the operation of a switchedmode power supply in terms of the following blocks: switched oscillator, transformer, rectifier, smoother, comparator, reference (including the use of opto-isolators to switch the oscillator on and off);

- (m) understand the operation of a dc voltage regulator in terms of the following blocks: reference, comparator, MOSFET follower.

## 4.4 Microcontroller Systems

A microcontroller system contains a number of blocks connected by buses.

Candidates should be able to:

- (a) understand the operation of a microcontroller system in terms of the following blocks: CPU, memory, input port, output port, clock, reset;

- (b) understand the use of the address, data and control buses to transfer data between the CPU and memory, input ports and output ports;

- (c) understand the use of the following registers in the CPU: program counter, stack pointer, general purpose registers;

- (d) recall the use of tristates and D flip-flops to construct input and output ports;

- (e) understand how in each machine cycle the CPU fetches an instruction from the memory and executes it, including changes in the contents of its registers;

- (f) understand the changes in the program counter when jump instructions are executed;

- (g) recall why the program counter is reset when the CPU's reset pin is activated;

- (h) understand that programs are stored in memory as hexadecimal code produced by compilers from programs written in other languages such as assembler and C.

The behaviour of a microcontroller depends on the program in its memory.

Candidates should be able to understand the use of the instruction set given in Appendix E to:

- loop until a required condition at the input port is met, including the use of the AND operation for selective resetting of bits (masking);

- (j) provide a time delay by counting down in a register until it reaches 00<sub>H</sub>;

- (k) fetch a byte from a look-up table and copy it to the output port;

- (I) use the EOR operation to selectively invert bits in the accumulator:

- (m) process a byte at the input port to generate an address for a look-up table;

- (n) shift bytes in the accumulator to the left or right:

- (o) the use of conditional and unconditional jumps, including the need for relative addressing;

- (p) call and return from subroutines, using registers to transfer information.

Programs can be made from subroutines.

- (q) recall that the stack is an area of memory for storing the contents of the program counter on a last-in, first-out (LIFO) basis;

- (r) understand the changes in the stack pointer and program counter when calling and returning from subroutines;

- (s) understand the advantages of designing programs from subroutines;

- (t) use the instruction set given in Appendix E to write subroutines, using registers to transfer data to and from the main program.

# 3.5 A2 Unit F615: Communication Systems

This unit introduces candidates to the use of electronic systems for communications. This includes the use of:

- trains of digital signals to display moving pictures on video screens;

- modulation to allow signals to be encoded onto high frequency carriers;

- frequency multiplexing to allow many carriers to be transmitted across a link;

- time division multiplexing to allow many sets of digital signals down a single link.

#### 5.1 Video Displays

Rapidly changing digital signals are used to display moving pictures on screens.

- (a) recall that video screens display colour pictures as lines of pixels in a frame, with separate red, green and blue pixels;

- (b) recall that the intensity of each pixel in a computer monitor is controlled by an analogue signal;

- (c) understand the need for raster scans, line synchronisation signals and frame synchronisation signals;

- (d) recall that the separate signals for red, green, blue, line sync and frame sync pass from a computer to a monitor;

- (e) understand that the frame refresh rate has to be about 25 Hz for a flicker-free moving image;

- (f) recall how to calculate the bandwidth required for a monitor cable from the refresh rate and the number of pixels per frame;

- (g) understand that a binary word can be used to determine the intensity of a pixel, including the relationship between the word length and the number of intensity levels;

- (h) recall how to calculate the bit rate required for a digital video stream from the bits per pixel, pixels per frame and the frame refresh rate;

- (i) understand that the bandwidth required for a digital video stream is half the bit rate;

- recall that compression of a digital image reduces the bits per frame but may result in a loss of quality.

## 5.2 Modulating Carriers

The amplitude of a high-frequency carrier can be modulated to carry information about a signal.

Candidates should be able to:

- (a) understand that amplitude modulation (AM) requires the amplitude of the carrier to carry information about the instantaneous voltage of the signal;

- (b) understand the use of a variable gain amplifier to produce AM carriers;

- (c) recall how to construct voltage—time and amplitude—frequency graphs of AM carriers (including the presence of sidebands on either side of the carrier);

- (d) understand the use of a rectifier and filter (diode detector) to recover a signal from an AM carrier:

- (e) recall and use the rule that the bandwidth required for an amplitude modulate signal is twice the maximum signal frequency.

The frequency of a high-frequency carrier can be modulated to carry information about a signal.

- understand that frequency modulation (FM) requires the frequency of the carrier to carry information about the instantaneous voltage of the signal;

- (g) understand the use of a variable frequency oscillator to produce FM carriers;

- (h) understand the use of a monostable and treble cut filter for frequency demodulation;

- recall how to construct voltage—time graphs of frequency modulated carriers;

- (j) recall and use the rule that the bandwidth required for an FM carrier is about five times the maximum frequency of the signal.

Pulse width modulation uses a digital signal to carry analogue information.

Candidates should be able to:

- (k) understand that the mark-space ratio of a pulse-width modulated (PWM) carrier is determined by the instantaneous voltage of the signal;

- (I) understand the use of a triangle waveform generator and a comparator to produce PWM carriers;

- (m) understand the operation of an op-amp ramp generator and an op-amp non-inverting Schmitt trigger to make a triangle waveform generator (including calculations of trip points and ramp rates from component values);

- (n) understand the need to sample the signal at least twice in each cycle (Nyquist criteria);

- (o) understand the use of a treble cut filter to demodulate a PWM carrier;

- (p) recall and use the rule that the bandwidth of a PWM carrier is about half the highest frequency present in the carrier.

Modulated carriers pick up noise and interference in transmission.

- (q) recall that modulated carriers can be transmitted as electrical signals along cables, as infrared along optical fibre or as radio waves;

- (r) understand that the intensity of a modulated carrier decreases with increasing distance of transmission (no quantitative details required);

- (s) understand that noise is a random signal that is added to modulated carriers in transmission;

- understand that interference is a signal from another carrier that is added to modulated carriers;

- (u) understand the relative susceptibility of twisted-pair cables, optical fibres and radio waves to noise and interference:

- (v) understand the meaning of signal-to-noise ratio (no quantitative details required);

- (w) understand the use of limiters/Schmitt triggers to remove noise and interference from FM and PWM carriers, including that this is not possible for AM carriers.

#### 5.3 Frequency Division Multiplexing

Many modulated carriers can be sent down a link by allocating each one to a different channel.

Candidates should be able to:

- (a) understand that frequency division multiplexing (FDM) allocates a different range of frequencies (channel) for each modulated carrier;

- (b) understand how the maximum number of channels in a link is related to its bandwidth and the bandwidth allocated to each channel;

- (c) recall the use of a parallel LC circuit and a resistor as a bandpass filter (including the effect on the bandwidth of increasing the resistance in the parallel LC circuit);

- (d) recall and use the equations for the reactance of an inductor ( $X_L = 2\pi fL$ ) and a capacitor ( $X_C = \frac{1}{2\pi fC}$ ), including the use of log–log plots of reactance against frequency to represent these characteristics:

- (e) recall and use the equation for the resonant frequency (  $f_0 = \frac{1}{2\pi\sqrt{LC}}$  ) of a parallel LC circuit;

- (f) understand the use of three stacked filters to make a bandpass filter with a flat top and sharp edges, including the need for buffer amplifiers between stages.

Radio transmissions use FDM.

- (g) understand the use of a tuned circuit at the base of an aerial to select a modulated carrier from just one broadcast channel;

- (h) recall that increasing the resistance in parallel with the tuned circuit increases the signal and reduces its bandwidth;

- recall the operation of a simple AM radio receiver in terms of the following blocks: aerial, tuned circuit, rf amplifier, diode demodulator, af amplifier, loudspeaker;

- (j) understand that the selectivity of a radio receiver is its ability to reject modulated carriers from neighbouring channels;

- (k) understand that the sensitivity of a radio receiver is its ability to pick up weak stations;

- (I) understand the operation of a superhet radio receiver in terms of the following blocks: aerial, tuned circuit, local oscillator, mixer, if filter, if amplifier, demodulator, af amplifier, loudspeaker.

## 5.4 Time Division Multiplexing

Telephone systems use time division multiplexing to make efficient use of links.

- (a) understand the operation of a digital transmission system in terms of the following blocks: analogue-to-digital converter (ADC), parallel-to-serial converter (PSC), serial-toparallel converter (SPC), digital-to-analogue converter (DAC);

- (b) understand that an ADC represents the signal voltage of each sample as a binary word, with the sampling rate at least twice the maximum signal frequency;

- understand the meaning of the terms range, resolution and sample rate as applied to ADCs;

- (d) understand the operation of flash ADCs made from comparators and logic gates;

- (e) recall the use of summing amplifiers as DACs, including calculating the range and resolution from the resistor values;

- (f) understand the operation of an ADC made from a binary counter, a comparator and a DAC, including its advantages and disadvantages compared with a flash converter;

- (g) understand how time-division multiplexing (TDM) allows many channels to share the same link;

- (h) understand that the bandwidth required for TDM is half the total bit rate;

- (i) understand the use of multiplexers and demultiplexers in TDM.

Computers exchange information along cables using time-division multiplexing.

- (j) understand that computers can exchange information with each other along a twistedpair cable by packets of serial digital signals;

- (k) understand that each packet contains the following information: the source address, the destination address, the data payload, checksum;

- understand the use of analogue switches to allow many systems to place signals on a single link in turn;

- (m) recall that each computer waits until there is no traffic on the cables before it attempts to transmit a packet;

- (n) understand the need for start (0) and stop (1) bits at the start and end of each packet;

- (o) understand the use of D flip-flops and logic gates to construct parallel-in serial-out (PISO) and serial-in parallel-out (SIPO) shift registers;

- (p) understand the use of shift registers in PTS and STP converters, including the need to use crystal oscillators;

- (q) recall that the bandwidth of the cable is half the maximum bit rate.

# 3.6 A2 Unit F616: Design, Build and Investigate Electronic Circuits

At A2 Level, the investigation consists of a complete project in which candidates design, build, test and analyse a circuit that could serve a useful purpose. This is expected to take between 15 and 20 hours of laboratory time with all work being carried out in the centre and a log/diary kept to record of circuit designs testing etc. Candidates also write a report that is marked by the centre and externally moderated by OCR. The assessment criteria are given in Appendix D.

#### **Project details**

The project should be a circuit that could serve a useful purpose and enables candidates access to the full range of marks available from the assessment criteria. Suggested project titles are given in Appendix E. OCR will give advice on the choice of projects if requested; requests should be made as early as possible in the academic year.

The project is expected to be constructed using a subsystem approach and the level should reflect the nature of the work done at A2. It is acceptable that the project be comprised of subsystems that represent aspects of the work done at both AS and A2 Level.

Once the project title has been determined, the candidate is expected to create a full set of specifications for the final circuit. This focuses the candidate on the design – build – test – analyse cycle. Candidates should recognise this from the preparatory work done in the AS Level investigation, and be able to apply the skills acquired to the full project at A2 Level. Emphasis is placed on the electronic principles involved and not on the quality of the finish, although there are marks available for neatness. As such, projects are expected to be built on prototype board/breadboard so that circuit build can be assessed. Projects are not expected to be built on PCB or with the use of modular kits.

#### Requirements

The project must have, at least three different subsystems, with more marks available for a project that consists of five or more subsystems. For the purposes of project design, a subsystem is an electronic circuit that has an active component. The use of microcontrollers is encouraged but this is considered to be a single subsystem. This is to discourage the production of a project that is solely based around a microcontroller and the project becoming an exercise in programming only.

Candidates should not work with a circuit that involves mains voltage.

All practical work undertaken on the project must be completed in the centre. Candidates are expected to focus on the design – build – test – analyse cycle and the report of the project should contain evidence of this cycle.

A diary/logbook should be kept by the candidate and kept up to date throughout the project completion. It is expected that this would be used by candidates to keep a record of circuit designs, testing procedures, etc. This is also where any reference material obtained by the candidate would be placed. Reference material should include any help obtained from websites. The candidate is expected to print a copy of the relevant page from the website used and keep this copy in the diary/logbook. The diary/logbook to be held centrally by the centre and made available to the moderator upon request.

#### The report

Each candidate prepares a written report of the project construction from initial design concept to final analysis. The report is expected to be no more than 2500 words. Emphasis is placed on the design – build – test – analyse cycle and, as such, the report should contain evidence of this cycle applied to each subsystem that comprises the final circuit. The report should be well written and contain the evidence that supports the use of the design – build – test – analyse cycle. The report should begin with a project title and a brief summary of the project (no more than 200 words), stating the purpose of the circuit, its design construction and whether or not the final circuit was completed successfully.

The report should also contain a clear, A4 size colour photograph of the final circuit as the moderator will be able to assess the project build from this. Graphs, tables and diagrams should be clearly presented and inserted in the appropriate place in the text. Irrelevant information (IC data sheets, etc) is not required; if the information is relevant, it is sufficient to quote it in the report. Each page should be numbered and the completed report should be stapled in the top left hand corner only; no further binding is required.

#### **Assistance**

It is recognised that some candidates need help in the production of a project. However, teachers must be careful not to give more assistance than is strictly necessary for the candidate to make progress. Where direct intervention by the teacher has been necessary, either in the design stage, the build stage or the testing/analysis stage, then this should be noted by the teacher. Some of the marks available in the assessment criteria reflect the amount of help given to candidates.

#### **Assessment**

The teacher assesses the report of the project under six headings:

- Introduction and Planning

- Circuit Design

- Understanding of Circuit Operation

- Circuit Build

- Testing and Analysis

- The Report.

There are 60 marks available. The teacher marks the report and annotates the report clearly by indicating where it is felt criterion have been achieved. A simple mark in red ink is sufficient to highlight the evidence for the mark awarded with a reference to the particular criterion. It is important to annotate the reports in such a manner as this aids both the teacher and the moderator in identifying the evidence for particular marks awarded.

#### Moderation and internal standardisation

It is the responsibility of the centre to carry out internal standardisation where two or more teachers have been responsible for the assessment of projects. A single reliable order of merit must be produced.

Projects should not be dismantled until they have been photographed and the internal assessment process (and, if necessary, the internal standardisation process) has been completed.

Following internal standardisation, marks are transferred to form MS1 and submitted to OCR by a specified date. Postal moderation then takes place.

For centres with ten or fewer candidates, the centre sends the form MS1 and all reports to the moderator. For centres with more than ten candidates, the centre sends the form MS1 only. Upon receipt of this, the moderator will then contact the centre and request a sample of the reports. The moderator may also request that the log books/diaries are also included in the sample.

# 4 Schemes of Assessment

# 4.1 AS GCE Scheme of Assessment

## AS GCE Electronics (H065)

#### AS Unit F611: Simple Systems

36.5% of the total AS GCE marks Candidates answer all questions.

1.5 h written paper

90 marks

This paper consists of short answer questions, calculations and extended written answers. Quality of written communication will be assessed in this paper.

### AS Unit F612: Signal Processors

36.5% of the total AS GCE marks Candidates answer all questions.

1.5 h written paper

90 marks

This paper consists of short answer questions, calculations and extended written answers, Quality of written communication will be assessed in this paper.

# AS Unit F613: Build and Investigate

27% of the total AS GCE marks Recommended 5 hours of lab time per task plus teaching time 80 marks The investigation consists of three short tasks. The three areas of work are set by OCR but the actual tasks based on these areas of work are chosen by the candidate in conjunction with the teacher. The work is internally marked with reference to an OCR mark scheme. Each task is marked individually, but only one set of marks is submitted.

Quality of written communication is marked at specific points throughout the assessment criteria unit.

**Assessment Criteria**: please refer to Appendix B at the end of this specification.

# 4.2 Advanced GCE Scheme of Assessment

#### Advanced GCE Electronics (H465)

AS Units as above, with each of Units F611 and F612 being 18.25% of the total Advanced GCE marks, and Unit F613 being 13.5% of the Advanced GCE marks.

#### A2 Unit F614: Electronic Control Systems

18.25% of the total Advanced GCE marks 1 h 40 min written

paper 110 marks Candidates answer all questions.

This paper consists of short answer questions, calculations and extended written answers. Quality of written communication will be assessed in this paper. The questions draw on the knowledge gained in unit F614 and the AS units.

This unit is synoptic.

## A2 Unit F615: Communications Systems

18.25% of the total Advanced GCE marks 1 h 40 min written paper 110 marks Candidates answer all questions.

This paper consists of short answer questions, calculations and extended written answers. Quality of written communication will be assessed in this paper. The questions draw on the knowledge gained in Unit F615 and the other units.

This unit is synoptic.

#### A2 Unit F616: Design, Build and Investigate

13.5% of the total Advanced GCE marks 15 hours coursework 60 marks The investigation consists of a single electronics project. The electronics project is chosen by the candidate and centre. The work is internally marked with reference to an OCR mark scheme and moderated by OCR. Quality of written communication is marked at specific points throughout the assessment criteria of this unit.

This unit is synoptic

**Assessment Criteria**: please refer to Appendix D at the end of this specification.

## 4.3 Unit Order

The normal order in which the unit assessments could be taken is AS Units F611, F612 and F613 in the first year of study, leading to an AS GCE award, then A2 Units F614, F615 and F616 leading to the Advanced GCE award. However, the unit assessments may be taken in any order.

Alternatively, candidates may take a valid combination of unit assessments at the end of their AS GCE or Advanced GCE course in a 'linear' fashion.

# 4.4 Unit Options (at AS/A2)

There are no optional units in the AS GCE specification; for AS GCE Electronics candidates must take AS Units F611, F612 and F613.

There are optional units in the Advanced GCE specification; for Advanced GCE Electronics candidates take AS Units F611, F612 and F613 and A2 Units F614, F615 and F616.

# 4.5 Synoptic Assessment (A Level GCE)

Synoptic assessment tests the candidates' understanding of the connections between different elements of the subject.

All A2 units require candidates to apply knowledge from units studied previously. The AS investigation requires knowledge gained from the AS units and the A2 investigation requires knowledge from all the previous units. The A2 written papers are structured to link areas previously studied at AS to the A2 units, the knowledge gained at AS being assessed at the A2 level.

# 4.6 Assessment Availability

There is one examination series each year in June.

From 2014, both AS units and A2 units will be assessed in June only.

#### 4.7 Assessment Objectives

Candidates are expected to demonstrate the following in the context of the content described:

#### AO1 Knowledge and Understanding

- recognise, recall and show understanding of scientific knowledge;

- select, organise and communicate relevant information in a variety of forms.

#### AO2 Application of Knowledge and Understanding

- analyse and evaluate scientific knowledge and processes;

- apply scientific knowledge and processes to unfamiliar situations including those related to issues;

- assess the validity, reliability and credibility of scientific information.

#### AO3 How Science Works

- demonstrate and describe ethical, safe and skilful practical techniques and processes, selecting appropriate qualitative and quantitative methods;

- make, record and communicate reliable and valid observations and measurements with appropriate precision and accuracy;

- analyse, interpret, explain and evaluate the methodology, results and impact of their own and others' experimental and investigative activities in a variety of ways.

AO weightings in AS GCE

| Unit                                                    | 9/   | % of AS GC | E   | Total |

|---------------------------------------------------------|------|------------|-----|-------|

|                                                         | AO1  | AO2        | AO3 | Total |

| AS Unit F611: Simple Systems                            | 18.5 | 18         | 0   | 36.5% |

| AS Unit F612: Signal Processors                         | 18.5 | 18         | 0   | 36.5% |

| AS Unit F613: Build and Investigate Electronic Circuits | 0    | 0          | 27  | 27%   |

|                                                         | 37%  | 36%        | 27% | 100%  |

AO weightings in Advanced GCE

| Unit                                                               | % of |     |      |        |  |  |

|--------------------------------------------------------------------|------|-----|------|--------|--|--|

|                                                                    | AO1  | AO2 | AO3  | Total  |  |  |

| AS Unit F611: Simple Systems                                       | 9.25 | 9   | 0    | 18.25% |  |  |

| AS Unit F612: Signal Processors                                    | 9.25 | 9   | 0    | 18.25% |  |  |

| AS Unit F613: Build and Investigate Electronic Circuits            | 0    | 0   | 13.5 | 13.5%  |  |  |

| A2 Unit F614: Electronic Control Systems                           | 7.25 | 11  | 0    | 18.25% |  |  |

| A2 Unit F615: Communications Systems                               | 7.25 | 11  | 0    | 18.25% |  |  |

| A2 Unit F616: Design, Build and Investigate<br>Electronic Circuits | 0    | 0   | 13.5 | 13.5%  |  |  |

| Total GCE weightings                                               | 33%  | 40% | 27%  | 100%   |  |  |

#### 4.8 Quality of Written Communication

Quality of written communication is assessed in all units and credit may be restricted if communication is unclear.

#### Candidates will:

- ensure that text is legible and that spelling, punctuation and grammar are accurate so that meaning is clear;

- select and use a form and style of writing appropriate to purpose and to complex subject matter;

- organise information clearly and coherently, using specialist vocabulary when appropriate.

The written papers will assess quality of written communication through questions that require some extended writing. There is a section in the mark scheme that is banded where the quality of written communication will be assessed, with marks being awarded for clarity, fluency and structure of the ideas expressed.

The practical units at AS and A2 (F613 and F616) have specific points in the marking criteria that assess the quality of written communication, with marks being awarded for structure of the reports and the clarity of written communication.

### 5 Technical Information

#### 5.1 Making Unit Entries

Please note that centres must be registered with OCR in order to make any entries, including estimated entries. It is recommended that centres apply to OCR to become a registered centre well in advance of making their first entries. Centres must have made an entry for a unit in order for OCR to supply the appropriate forms or moderator details for coursework.

It is essential that unit entry codes are quoted in all correspondence with OCR.

For the moderated coursework units F613 and F616, candidates must be entered for either the OCR Repository option or the postal moderation option. Centres must enter all of their candidates for **one** of the options. It is not possible for centres to offer both components within the same series.

| Unit entry code | Component code | Assessment method               | Unit title                         |

|-----------------|----------------|---------------------------------|------------------------------------|

| F611            | -              | Written paper                   | Simple Systems                     |

| F612            | -              | Written paper                   | Signal Processors                  |

| F613            | 01             | Moderated via OCR<br>Repository | Build and Investigate              |

| F613            | 02             | Moderated via postal moderation | Electronic Circuits                |

| F614            | -              | Written paper                   | Electronic Control<br>Systems      |

| F615            | -              | Written paper                   | Communication<br>Systems           |

| F616            | 01             | Moderated via OCR<br>Repository | Design, Build and                  |

| F616            | 02             | Moderated via postal moderation | Investigate Electronic<br>Circuits |

#### 5.2 Making Qualification Entries

Candidates must enter for qualification certification separately from unit assessment(s). If a certification entry is **not** made, no overall grade can be awarded.

Candidates may enter for:

- AS GCE certification (entry code H065).

- Advanced GCE certification (entry code H465).

A candidate who has completed all the units required for the qualification, and who did not request certification at the time of entry, may enter for certification either in the same examination series (within a specified period after publication of results) or in a later series.

AS GCE certification is available from June 2014.

Advanced GCE certification is available from June 2014.

#### 5.3 Grading

All GCE units are awarded a-e. The Advanced Subsidiary GCE is awarded on the scale A-E. The Advanced GCE is awarded on the scale A-E with access to an A\*. To be awarded an A\*, candidates will need to achieve a grade A on their full A level qualification and an A\* on the aggregate of their A2 units. Grades are reported on certificates. Results for candidates who fail to achieve the minimum grade (E or e) will be recorded as *unclassified* (U or u) and this is **not** certificated.